Energy Efficient VLSI and Arithmetic

| |

|

| |

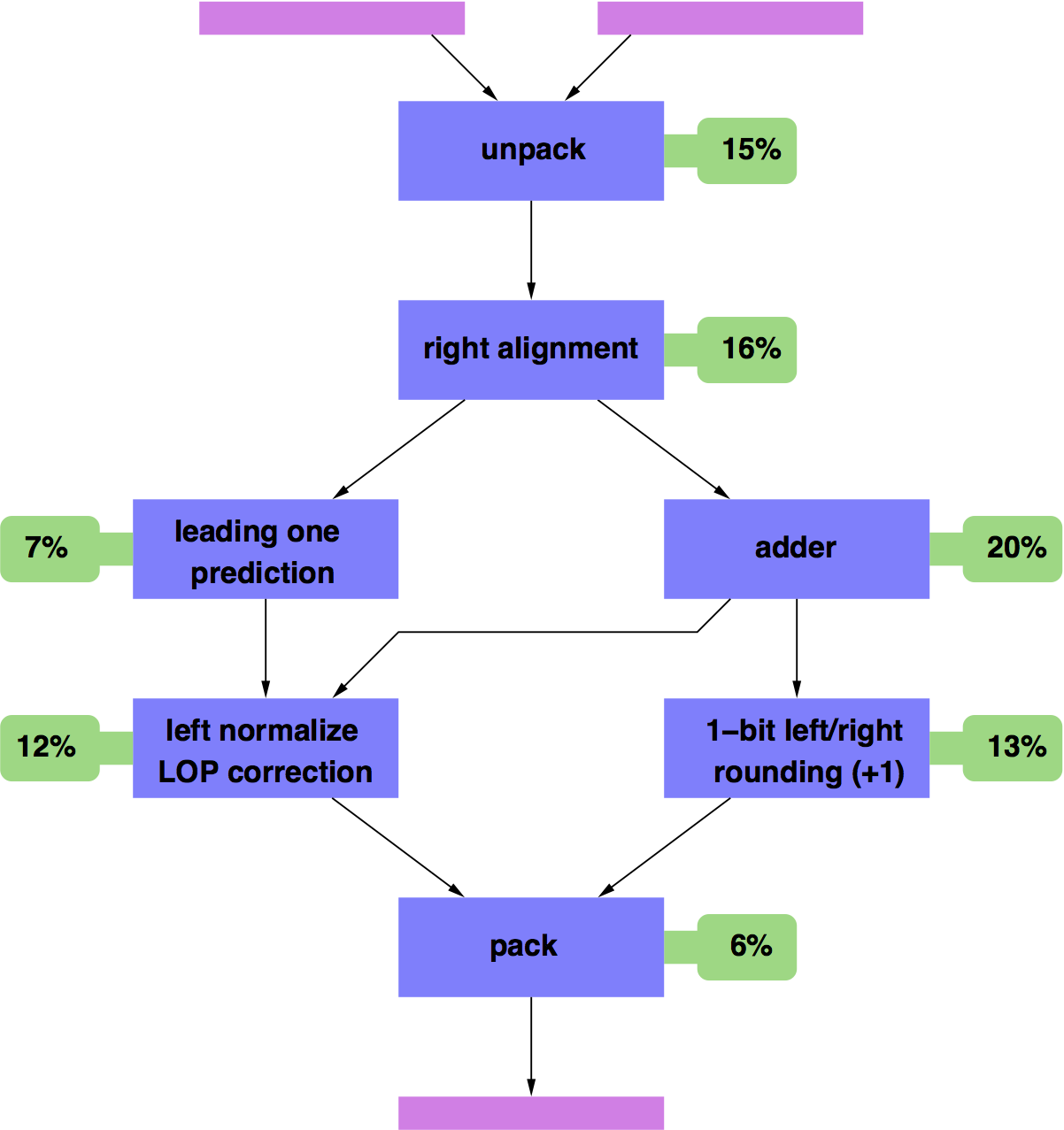

FPA design |

Eliminating a global clock provides a path to optimizing arithmetic

circuits and other building blocks for the expected delay rather

than the maximum delay. In some cases this can lead to significant

improvement in either energy or performance. We are examining the impact

of asynchrony on common building blocks in digital VLSI systems.

- Students

- Edward Bingham

- David Fang (Ph.D. 2008)

- Julia Karl (M.S. 2015)

- Praful Purohit

- Jonathan Tse (Ph.D. 2015)

- Basit Riaz Sheikh (Ph.D. 2011)

- Publications

- Rajit Manohar.

Comparing Stochastic and Deterministic Computing.

IEEE Computer Architecture Letters, 14(2):119--122, July 2015.

(abstract, pdf) — Best of Computer Architecture Letters

- Jonathan Tse, Benjamin Hill, and Rajit Manohar.

A Bit of Analysis on Self-Timed Single-Bit On-Chip Links.

Proceedings of the 19th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2013.

(abstract, pdf)

- Benjamin Tang, Stephen Longfield, Rajit Manohar, and Sunil Bhave.

Low Power ASIC GPS Tracking Loops: Quantifying the Trade-Offs Between Area, Power and Accuracy.

Proc. ION GNSS Technical Meeting, September 2012.

— Best presentation award

- Basit Riaz Sheikh and Rajit Manohar.

An Asynchronous Floating-Point Multiplier.

Proceedings of the 18th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2012.

(abstract, pdf)

- Basit Riaz Sheikh and Rajit Manohar.

Energy-efficient Pipeline Templates for High Performance Asynchronous Circuits.

ACM Journal on Emerging Technologies in Computer Systems (special issue on asynchrony in system design), 7(4), December 2011.

(abstract, pdf)

- Basit Riaz Sheikh and Rajit Manohar.

An Operand-Optimized Asynchronous IEEE 754 Double-precision floating-point adder.

Proceedings of the 16th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2010.

(abstract, pdf) — Best paper award

- Carlos Tadeo Ortega Otero, Jonathan Tse, and Rajit Manohar.

Static Power Reduction Techniques for Asynchronous Circuits.

Proceedings of the 16th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2010.

(abstract, pdf)

- Christopher LaFrieda and Rajit Manohar.

Reducing Power Consumption with Relaxed Quasi Delay-Insensitive Circuits.

Proceedings of the 15th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), May 2009.

(abstract, pdf)

- David Fang, Filipp Akopyan, and Rajit Manohar.

Self-Timed Thermally Aware Circuits.

IEEE Computer Society Annual Symposium on VLSI (ISVLSI), March 2006.

(abstract, pdf)

- David Fang and Rajit Manohar.

Non-Uniform Access Asynchronous Register Files.

Proceedings of the 10th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), April 2004.

(abstract, pdf, ps)

- John Teifel and Rajit Manohar.

A High Speed Clockless Serial Link Tranceiver.

Proceedings of the 9th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), pp. 151--161, Vancouver, BC, May 2003.

(abstract, pdf, ps)

- Virantha Ekanayake and Rajit Manohar.

Asynchronous DRAM Design and Synthesis.

Proceedings of the 9th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), pp. 174--183, Vancouver, BC, May 2003.

(abstract, pdf, ps)

- John Teifel, David Fang, David Biermann, Clinton Kelly IV, and Rajit Manohar.

Energy-Efficient Pipelines.

Proceedings of the 8th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), pp. 21--31, Manchester, UK, March 2002.

(abstract, ps)

- Rajit Manohar.

Width-Adaptive Data Word Architectures.

Proceedings of the 19th Conference on Advanced Research in VLSI (ARVLSI), pp. 112--129, Salt Lake City, Utah, March 2001.

(abstract, pdf, ps)

- Rajit Manohar.

The Entropy of Traces in Parallel Computation.

IEEE Transactions on Information Theory, 45(5):1606--1608, July 1999.

(abstract, pdf, ps)

- Rajit Manohar and José A. Tierno.

Asynchronous Parallel Prefix Computation.

IEEE Transactions on Computers, Vol. 47, No. 11, 1244-1252, November 1998.

(abstract, ps)

|