# PROFILING INFRASTRUCTURE FOR THE PERFORMANCE EVALUATION OF ASYNCHRONOUS SYSTEMS

#### A Dissertation

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of Jedi Master of Philosophy

by

David C. Fang

August 2008

© 2008 David C. Fang

ALL RIGHTS RESERVED

# PROFILING INFRASTRUCTURE FOR THE PERFORMANCE EVALUATION OF ASYNCHRONOUS SYSTEMS

David C. Fang, Ph.D.

Cornell University 2008

Designing and optimizing large-scale, asynchronous circuits is often an iterative process that cycles through synthesis, simulating, benchmarking, and program rewriting. Asynchronous circuits are usually specified by high-level, sequential or concurrent programs that prescribe the intended behavior. The self-timed nature of the interface gives designers much freedom to refine and rewrite equivalent specifications for improved circuit synthesis. However, at any step in the design cycle, one faces an uncountable number of choices for program rewriting — one simply cannot afford to explore all possible transformations. Informed optimizations and design space pruning can require detailed knowledge of the run-time behavior of the program, which is what our simulation trace analysis infrastructure provides. Tracing entire simulations gives users the opportunity to understand program execution in great detail. Most importantly, trace profiling captures typical run-time behavior and input-dependent behavior that cannot always be inferred from static analysis. Profiling provides valuable feedback for optimizing both high-level transformations and low-level netlist synthesis.

To address this need for profiling, we present a framework for analyzing the simulated execution of high-level, concurrent programs, as a foundation for iterative optimization and synthesis of asynchronous circuits. The framework includes a Scheme environment and a library of primitive procedures for handling and querying trace data. Interactivity is essential for analysis sessions where the sequence of queries to execute is not known a priori. The initial library also includes procedures for some frequently run analyses (built on top of the primitives). Providing an interface for working directly with the simulation and trace data structures makes analysis development within our framework both flexible and convenient. The extensibility of our framework enables compilation-free development and prototyping of custom analysis routines, so users can easily share and build upon the work of others. The primary purpose of this analysis framework is to enable future tools to use profile-driven feedback in automating iterative optimization and design-space exploration.

#### BIOGRAPHICAL SKETCH

David is the son of Que-Tsang and Lee Fang, who emigrated from Taiwan as graduate students at the University of Illinois, Urbana-Champaign. He graduated from Franklin Regional Senior High School in Murrysville, PA with Honors with Highest Distinction in the class of 1997. He enrolled at the California Institute of Technology in 1997, ambitiously intending to tackle electrical engineering, physics, and a twist of applied mathematics, but graduated with only a Bachelor of Science in Electrical Engineering with Honors in 2001. He thanks his wise upperclassmen and peers at Caltech for dissuading him from attempting more than one major. David still reminisces about the times spent growing and learning at Caltech, that is, when he wasn't slaving away on projects and courses.

The roots of his interest in asynchronous VLSI trace back to the EE/CS181abc class he took as an undergraduate, taught by Prof. Alain Martin and his research group members. Once he grasped the beauty and purity of self-timed programming, he endeavored to make his contribution to the field. The author received a National Defense Science and Engineering Graduate Fellowship, sponsored by the Office of Naval Research. Since the summer of 2001, the author has been a student of the Computer Systems Laboratory in the Cornell Electrical and Computer Engineering Department, under the guidance of Prof. Rajit Manohar, a former student of Alain Martin. The change of climate was likened to leaping out of the frying pan and into the freezer.

To supplement his background in asynchronous VLSI, the author minored in computer science, and maintains interest in computer architecture and compilers, which spans the hardware and software aspects of computer engineering. He also maintains an interest in algorithms, numerical analysis, optimization problems, information theory, and mathematical puzzles. Aside from being passionate about his work, he also maintains strong interest in music and dance, which have deserved a lot more time than he has actually devoted.

David has already accepted a full-time job as an engineer at Achronix Semiconductor Corporation in San Jose, CA, with many of his current and former Cornell colleagues, where he aspires to help take asynchronous circuits to new limits.

David hates writing about himself in the third person, so rest assured that the remainder of this dissertation is not written in this awkward manner.

${\it dedicated \ to \ my \ grandparents},$  who have always held the highest expectations of me

#### ACKNOWLEDGMENTS

Graduate school is not *just* about cranking out research papers and earning another degree. Much of my education in graduate school was gained through discussions with talented and uniquely-minded colleagues. The most valuable times were spent socializing outside of work. You have all made my stay at Cornell a truly memorable experience. I would like to extend my sincerest gratitude (or give a shout out) to the following individuals and organizations.

Mainak, I didn't make our national Math Olympiad team either – thank you for sharing your passion for solving challenging problems. Daehyun, your passion with video games is contagious! Avneesh, the Source will always be with you. Prof. Mark Heinrich, Prof. Evan Speight, the early years of CSL were entertaining, thanks to your presence in the faculty! Ilya, don't say I didn't warn you about Compilers. Brian, you're patience with school gives hope to many students. Jonathan, your rants about wine and women were a welcome respite from the daily grind of research. Scott, graduate student manager and savior by day, maniacal drummer by night – we know who holds the *real* power!

Teifel, you were right about grad school, not that I had any doubts. Clint, no only do I have you to thank for my job, but my days in the office just would've lacked amusement without your wit and humor, even when the joke was on me. Virantha, thank you for introducing me to awk many years ago, choose carefully next time. Song, there's no shame in being the Beast-Master. Sandra and Brett, thank you for sharing your passion for cats, computers, and food. Biermann, the legend of the Drunken-Duck Style Master lives on. LaFrieda, you can count on me for a football match anytime. Paula and Basit, thank you for bringing life to our memorable social gatherings. Rob and Ben, your days of glory are just over the horizon. Filipp, your destiny awaits you even when you deny it, search your feelings, you know it to be true. Carlos Tadeo, your humility only earns you greater respect.

Prof. Martin Burtscher and Prof. Radu Rugina, thank you for serving on my committee during our years at Cornell; your feedback was always appreciated. Thank you, Prof. José Martínez and Prof. Dave Albonesi, for serving on my committee at the late hour, and especially for your constructive feedback and thoughtful questions. Prof. Rajit Manohar, thank you for your continued guidance, and always leading by good example for students and future educators. Your patience with me knows no limits, but I won't push it any longer!

Had it not been for my friends in Cornell Ballroom and Dancesport and the Ithaca Swing Dance Network, I would've gone crazy years ago. Thank you for the wonderful times and giving me an escape from work. These are the times I will miss the most in Ithaca. André, thank you for showing me that the road to success doesn't require long hours of work. Nate, Adriana, and Peter, thanks for tolerating my extended absences and odd hours at our humble apartment. Ellan, Sara, Heather, thank you for sharing many dances, travels, music, and hours of deep conversation over the years. Helen, your support and encouragement have

guided me through some of the difficult times in school, thank you for reinforcing my determination. Mom, Dad, Allison – thank you for bearing with me and my long absences from home, in the pursuit of higher education.

Finally much of my work in our research group is funded by: Department of Defense, American Society of Engineering Education, Office of Naval Research, Defense Advanced Research Projects Agency, and National Science Foundation. Their generous support continues to attract talent to undertake advanced research at institutes of higher education.

#### TABLE OF CONTENTS

| $\mathbf{B}^{i}$ | iogra                    | phical Sketch                   | ii                                                      |

|------------------|--------------------------|---------------------------------|---------------------------------------------------------|

| D                | edica                    | tion                            | iv                                                      |

| $\mathbf{A}$     | ckno                     | vledgments                      | v                                                       |

| Ta               | able (                   | of Contents                     | vi                                                      |

| Li               | $\mathbf{st}$ of         | Tables                          | X                                                       |

| Li               | $\mathbf{st}$ of         | Figures                         | X                                                       |

| Li               | $\mathbf{st}$ of         | Abbreviations                   | iv                                                      |

| P                | refac                    | 3                               | χī                                                      |

| 1                | 1.1<br>1.2<br>1.3<br>1.4 | Oduction Preliminary Background | 1<br>1<br>2<br>2<br>4<br>6<br>7                         |

| 2                | 2.1<br>2.2               | 2.2.1 Measurement and Tracing   | 9<br>10<br>10<br>12<br>13<br>14<br>14<br>14<br>16<br>17 |

| 3                | Per: 3.1 3.2             | Language and Compiler           | 18<br>18<br>19<br>19                                    |

| Δ | СН             | P Quick Reference                            | 93           |

|---|----------------|----------------------------------------------|--------------|

| 6 | Con            | nclusion                                     | 90           |

|   | 5.3            | Summary                                      | 89           |

|   | 5.2            | Bit-serial Routers                           | 82           |

| 5 | <b>App</b> 5.1 | plications: Case Studies Fibonacci Generator | <b>74</b> 74 |

|   | 4.7            | Application to Synthesis Optimization        | 73           |

|   |                | 4.6.4 Arbitration with Reordering            | 71           |

|   |                | 4.6.3 Nondeterministic Dispatching           | 69           |

|   |                | 4.6.2 Coalescing Transformation              | 64           |

|   |                | 4.6.1 Temporal Activity Analysis             | 63           |

|   | 4.6            | Replication vs. Coalescing                   | 62           |

|   | 4.5            | Selection Restructuring                      | 60           |

|   | 4.4            | Flow Control and Speculation                 | 57           |

|   | 4.3            | Subexpression Scheduling                     | 54           |

|   |                | 4.2.2 Token ring examples                    | 51           |

|   |                | 4.2.1 Intuition from criticality             | 51           |

|   | 4.2            | Pipelining and Slack Matching                | 49           |

| 4 | <b>App</b> 4.1 | Parallel Decomposition                       | <b>46</b> 47 |

|   |                |                                              |              |

|   | 3.7            | 3.6.5 Near-critical paths                    | 43<br>45     |

|   |                | 3.6.4 Critical path sensitivity              | 43           |

|   |                | 3.6.3 Slack time computation                 | 42           |

|   |                | 3.6.2 Critical path statistics               | 41           |

|   |                | 3.6.1 Algorithm and implementation           | 40           |

|   | 3.6            | Critical Path Analysis                       | 40           |

|   |                | 3.5.4 Combining static and trace analyses    | 39           |

|   |                | 3.5.3 Trace stream manipulation              | 38           |

|   |                | 3.5.2 Trace file streaming                   | 37           |

|   |                | 3.5.1 Trace file content access              | 36           |

|   | 3.5            | Trace analysis                               | 36           |

|   |                | 3.4.2 Using shared results                   | 35           |

|   |                | 3.4.1 Sharing and caching computed results   | 32           |

|   | 3.4            | Static analysis procedures and variables     | 30           |

|   |                | 3.3.2 Simulator structure and event queries  | 29           |

|   | 3.3            | Analysis Environment                         | 26<br>27     |

|   | 2.2            | 3.2.3 Execution Tracing                      |              |

|   |                | 2.2.2 Evacution Tracing                      | 25           |

| В            | CH   | P Prod | cess Library          | 94      |

|--------------|------|--------|-----------------------|---------|

|              | B.1  | Buffer | ·s                    | <br>94  |

|              | B.2  | Functi | ions                  | <br>94  |

|              | В.3  | Enviro | onments               | <br>95  |

|              | B.4  | Flow ( | Control               | <br>95  |

|              | B.5  | Altern | nators                | <br>96  |

| $\mathbf{C}$ | Sch  | eme U  | tility Library        | 98      |

|              | C.1  | Queue  | es                    | <br>98  |

|              | C.2  | Algori | thms                  | <br>98  |

|              | C.3  | Red-b  | lack Trees            | <br>100 |

|              | C.4  | Stream | ns                    | <br>102 |

| D            | HA   | C Obj  | ect File API          | 105     |

| ${f E}$      | HA   | с сні  | P Simulator State API | 106     |

| _            | E.1  | _      | retrieval             |         |

|              | E.2  |        | predicates            |         |

|              | E.3  |        | properties            |         |

|              | E.4  |        | omputed static data   |         |

|              | E.5  |        | analysis routines     |         |

|              |      | E.5.1  | Event graphs          |         |

|              |      | E.5.2  | Graph traversal       |         |

|              |      | E.5.3  | Event loops           |         |

|              |      | E.5.4  | Selection events      |         |

|              |      | E.5.5  | Concurrent sections   |         |

| $\mathbf{F}$ | НΔ   | C Simi | ulator Trace API      | 116     |

| •            |      |        | tives                 |         |

|              |      | F.1.1  | Event trace access    |         |

|              |      | F.1.2  | State trace access    |         |

|              | F.2  |        | dures                 |         |

|              |      | F.2.1  | Trace file operations |         |

|              |      | F.2.2  | State change traces   |         |

|              |      | F.2.3  | Critical path         |         |

|              |      | F.2.4  | Branch statistics     |         |

|              |      | F.2.5  | Loop statistics       |         |

|              |      | F.2.6  | Channel statistics    |         |

|              |      | F.2.7  | Process statistics    |         |

| Bi           | hlio | raphy  |                       | 127     |

#### LIST OF TABLES

| 4.1 | Critical path through a token ring, whose performance is limited by<br>the buffers' cycle time. Send-receive event pairs have been grouped |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | together                                                                                                                                   | 53 |

| 4.2 | Critical path through a token ring, whose performance is limited<br>by the buffers' forward latency. Send-receive event pairs have been    |    |

|     | grouped together.                                                                                                                          | 53 |

| 5.1 | Critical path through a minimum-slack Fibonacci loop (Figure 5.2)                                                                          | 78 |

| 5.2 | Critical path through a partially slack-matched Fibonacci loop (Fig-                                                                       |    |

|     | ure 5.3)                                                                                                                                   | 78 |

| 5.3 | Critical path through a fully slack-matched Fibonacci loop (Fig-                                                                           |    |

|     | ure 5.4)                                                                                                                                   | 79 |

| 5.4 | Summary of tradeoffs of three designs of Fibonacci loop                                                                                    | 81 |

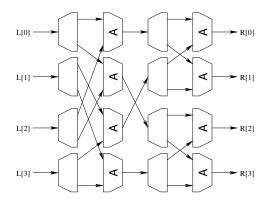

| 5.5 | Execution times of single (Figure 5.5) and twin (Figure 5.6) bit-                                                                          |    |

|     | serial routers under different input workloads                                                                                             | 84 |

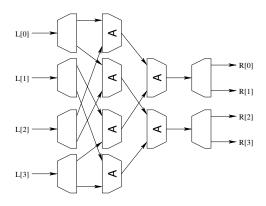

| 5.6 | Area and energy breakdown of various $(4,4)$ bit-routers. $K$ is the                                                                       |    |

|     | total length of a packet (number of symbols), $E_s$ is energy per                                                                          |    |

|     | symbol through a split, $E_m$ is energy per symbol through a merge.                                                                        | 87 |

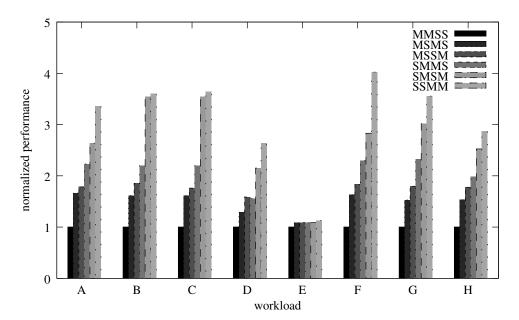

| 5.7 | Speedups of various implementations of (4,4) bit-serial routers rel-                                                                       |    |

|     | ative to the MMSS baseline, under different input workloads (see                                                                           |    |

|     | also Figure 5.13)                                                                                                                          | 88 |

#### LIST OF FIGURES

| 1.1                             | Asynchronous circuit synthesis flow                                   | 5                    |

|---------------------------------|-----------------------------------------------------------------------|----------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Syntax-directed translation of CHP to event graphs                    | 19<br>20<br>22<br>23 |

| 0.0                             | chronization between two processes; neither process can complete      |                      |

|                                 | its communication action until its counterpart has also been reached. | 23                   |

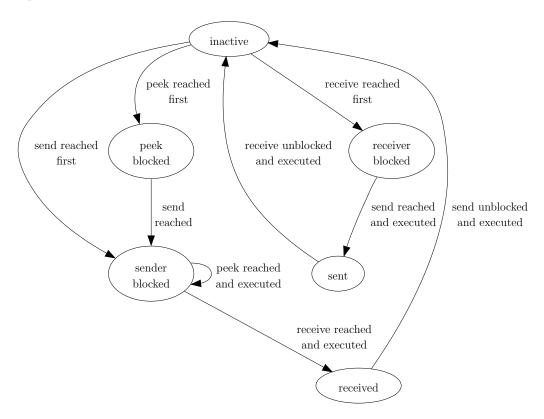

| 3.6                             | chpsim channel status changes, with peek                              | 24                   |

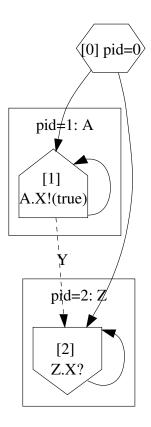

| 3.7                             | CHP whole program event graph for Program 3.1                         | 29                   |

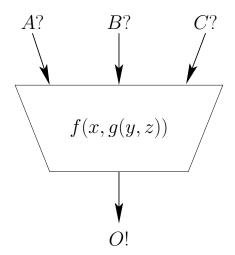

| 4.1                             | Unpipelined expression computation process                            | 48                   |

| 4.2                             | Pipelined expression computation process                              | 48                   |

| 4.3                             | Whole program event graph of a token ring                             | 52                   |

| 4.4                             | A balanced computation tree is suitable when inputs arrive close      |                      |

|                                 | in time.                                                              | 55                   |

| 4.5                             | An unbalanced computation tree is suitable when the last input        |                      |

| 1.0                             | arrives much later than the rest.                                     | 55                   |

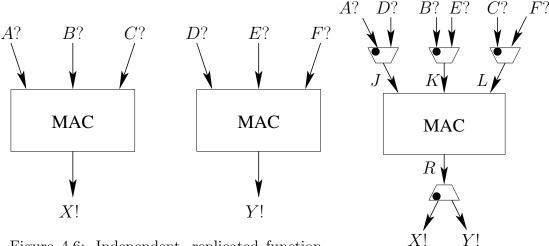

| 4.6                             | Independent, replicated function units can operate concurrently       | 65                   |

| 4.7                             | Single function unit shared in alternation                            | 65                   |

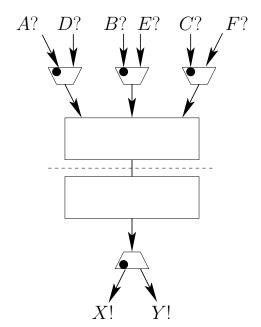

| 4.8<br>4.9                      | Pipelined function unit, shared in alternation                        | 68<br>68             |

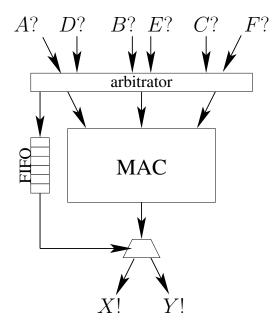

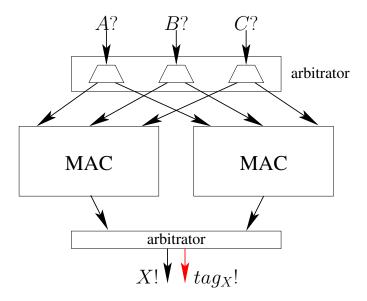

| 4.9                             | Single function unit shared by arbitration                            | UC                   |

|                                 | nators with a single-unit interface.                                  | 69                   |

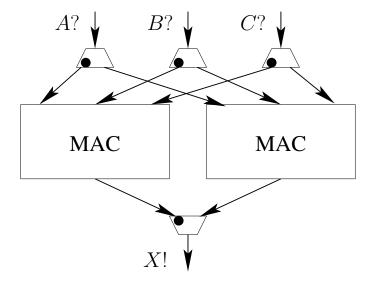

| 4.11                            | Arbitration can be used to dispatch operands to first-available pro-  |                      |

|                                 | cesses and to reorder results from replicated units                   | 72                   |

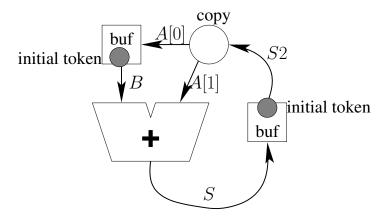

| 5.1                             | Schematic of a decomposed Fibonacci sequence generator                | 74                   |

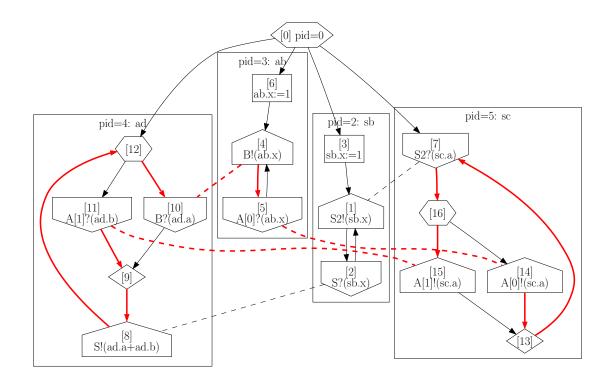

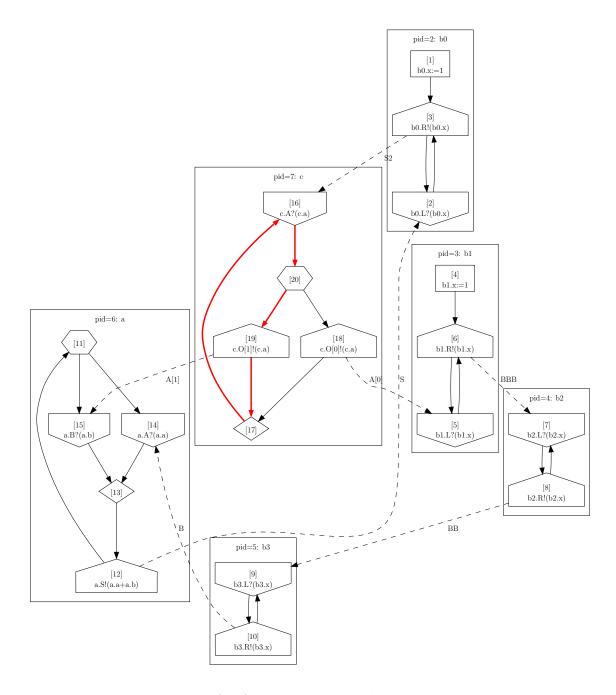

| 5.2                             | CHP event graph of initially decomposed Fibonacci sequence gen-       |                      |

|                                 | erator. Bold-red edges mark the critical path from Table 5.1          | 75                   |

| 5.3                             | Event graph of a partially slack-matched Fibonacci sequence gen-      |                      |

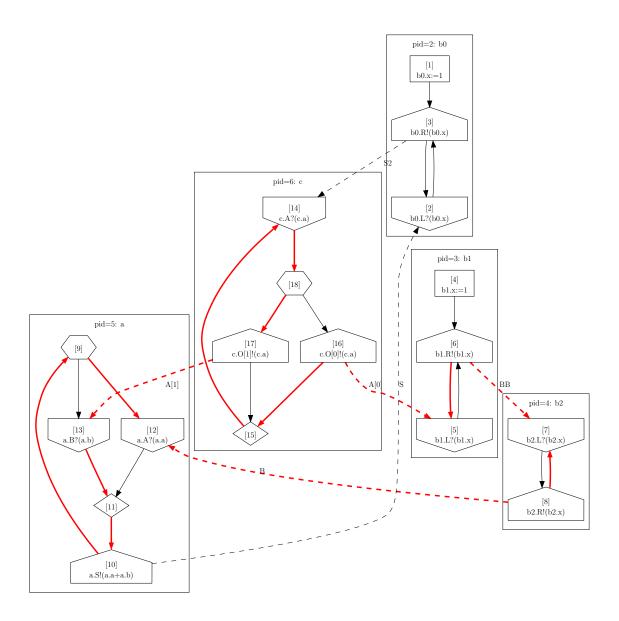

|                                 | erator. Bold-red edges mark the critical path from Table 5.2          | 76                   |

| 5.4                             | Event graph of a fully slack-matched Fibonacci sequence generator.    |                      |

|                                 | Bold-red edges mark the critical path from Table 5.3                  | 77                   |

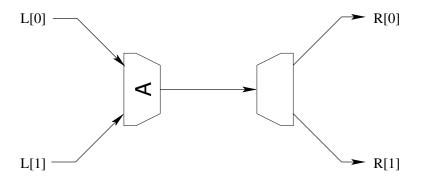

| 5.5                             | Schematic of a decomposed merge-split bit-serial router               | 82                   |

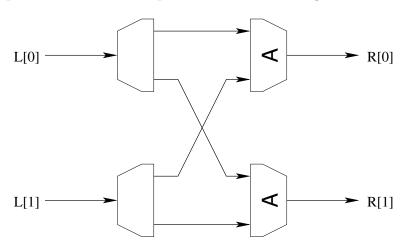

| 5.6                             | Schematic of a decomposed split-merge bit-serial router               | 83                   |

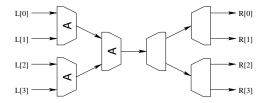

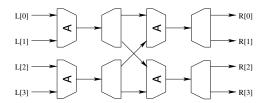

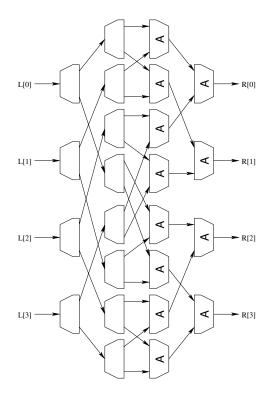

| 5.7                             | A merge-merge-split-split (4,4) bit-router                            | 85                   |

| 5.8                             | A merge-split-merge-split (4,4) bit-router                            | 85                   |

| 5.9                             | A merge-split-split-merge (4,4) bit-router                            | 85                   |

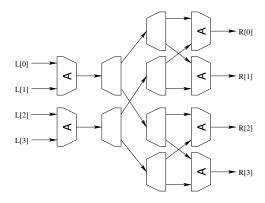

| 5.10                            | A split manus split manus (4.4) bit router                            | 86                   |

| 5.11                            | A split split merge (4,4) bit-router                                  | 86                   |

| 5.12                            | A split-split-merge-merge $(4,4)$ bit-router                          | 87                   |

| 5.13 | Performance of various (4,4) bit-serial routers, normalized to the |    |

|------|--------------------------------------------------------------------|----|

|      | MMSS baseline (see also Table 5.7)                                 | 88 |

#### LIST OF PROGRAMS

| 3.1  | Source connected to sink                                                               | 27  |

|------|----------------------------------------------------------------------------------------|-----|

| 3.2  | chpsim-find-events-involving-channel-id: Procedure to find                             |     |

|      | all static events that can affect the state of a channel                               | 31  |

| 3.3  | <pre>chpsim-event-loop-head? procedure</pre>                                           | 34  |

| 3.4  | <pre>chpsim-event-loop-tail? procedure</pre>                                           | 34  |

| 3.5  | Extract subset of event history on one particular event                                | 38  |

| 3.6  | Truncate a prefix of an event stream before a given time                               | 38  |

| 3.7  | Truncate a suffix of an event stream after a given time                                | 38  |

| 3.8  | Crop an event stream within a given time span                                          | 38  |

| 3.9  | Crop an state-change stream within a given event span                                  | 39  |

| B.1  | bool-buf CHP process                                                                   | 94  |

| B.2  | bool-buf-init CHP process                                                              | 94  |

| B.3  | bool-peekbuf CHP process                                                               | 94  |

| B.4  | bool-and CHP process                                                                   | 94  |

| B.5  | bool-table CHP process                                                                 | 95  |

| B.6  | bool-sink CHP process                                                                  | 95  |

| B.7  | bool-source CHP process                                                                | 95  |

| B.8  | bool-copy CHP process                                                                  | 95  |

| B.9  | bool-merge CHP process                                                                 | 95  |

| B.10 | bool-split CHP process                                                                 | 96  |

|      | bool-split-alternator CHP process                                                      |     |

| B.12 | bool-merge-alternator CHP process                                                      | 96  |

| B.13 | bool-parallel-fifo CHP process                                                         | 96  |

| E.1  | <pre>chpsim-filter-static-events procedure</pre>                                       | 109 |

| E.2  | ${\tt chpsim-filter-static-events-indexed} \ \ {\tt procedure}  . \ . \ . \ . \ .$     | 109 |

| E.3  | chpsim-assoc-event-successors procedure                                                | 109 |

| E.4  | static-event-successors-map-delayed variable                                           | 109 |

| E.5  | static-event-predecessors-map-delayed variable                                         | 110 |

| E.6  | chpsim-successor-lists->histogram variable                                             | 110 |

| E.7  | static-events-with-multiple-entries-delayed variable                                   | 110 |

| E.8  | $\verb static-events-depth-first-walk-predicated  procedure$                           |     |

|      | ${\tt static-events-depth-first-walk-iterative} \ \ {\tt procedure} \ \ . \ \ . \ \ .$ |     |

|      | static-loop-bound-events-delayed variable                                              |     |

| E.11 | static-do-while-bound-events-delayed delayed variable                                  | 113 |

|      | static-do-while-events-delayed variable                                                |     |

|      | static-branch-bound-events-delayed variable                                            |     |

| E.14 | static-fork-join-events-delayed variable definition                                    |     |

| F.1  | chpsim-state-trace-filter-reference: Procedure to filter a state-                      | -   |

|      | change stream with only events that affect a single variable (type,                    |     |

|      | index) pair                                                                            | 119 |

| F.2  | chpsim-state-trace-focus-reference: Procedure to focus state-       |    |

|------|---------------------------------------------------------------------|----|

|      | change on only the referenced variable, stripping away the unrefer- |    |

|      | enced variables that change on the same events                      | 20 |

| F.3  | chpsim-state-trace-single-reference-values: Procedure to strip      |    |

|      | away the variable index from a focused state-change stream, leaving |    |

|      |                                                                     | 20 |

| F.4  | chpsim-trace-critical-path-from: Procedure for extracting a         |    |

|      | critical path (stream) given a random-access event trace handle and |    |

|      |                                                                     | 21 |

| F.5  | chpsim-trace-critical-path: Combined procedure for opening          |    |

|      | an event trace, and extracting the critical path, starting from the |    |

|      | last event                                                          | 21 |

| F.6  | make-event-adjacency-histogram: Procedure for constructing an       |    |

|      | adjacency histogram given a stream of critical events               | 21 |

| F.7  | make-select-branch-histogram: Procedure to construct a his-         |    |

|      | togram of successors taken per branch                               | 22 |

| F.8  | make-loop-histogram: Procedure to construct a histogram of loop     |    |

|      | occurrences                                                         | 23 |

| F.9  | make-critical-channel-event-pairs-list: Procedure to fold and       |    |

|      | filter channel events from a critical path                          | 24 |

| F.10 | filter-critical-channel-event-pairs-list: Filter to keep only       |    |

|      | 1                                                                   | 25 |

| F.11 | count-send-receive-criticality: Procedure to count occurrences      |    |

|      | J.                                                                  | 25 |

| F.12 | channel-send-receive-criticality: Composed procedure to count       |    |

|      | occurrences of sender or receiver criticality                       | 25 |

| F.13 | make-critical-process-histogram: Procedure to identify which        |    |

|      | 1                                                                   | 26 |

| F.14 | print-named-critical-process-histogram: Print name of pro-          |    |

|      | cess along with index and number of occurrences on the critical     |    |

|      | path from the given histogram                                       | 26 |

#### LIST OF ABBREVIATIONS

AFPGA asynchronous FPGA

API application program interface

ASIC application-specific integrated circuit

AVLSI asynchronous VLSI

CAD computer-aided design/development

CFG control flow graph

CHP Concurrent Hardware Processes

CSP Communicating Sequential Processes

EDA electronic design automation FPGA field-programmable gate array

GNU GNU is not Unix

HAC Hierarchical Asynchronous Circuits (HAC)

HDL hardware description language

HSE handshaking expansion

PRS production rule set

QDI quasi-delay insensitive

RTL register transfer logic

SDT syntax-directed translation

STA static timing analysis

VHDL VHSIC Hardware Description Language VHSIC Very High Speed Integrated Circuits

VLSI very large scale integration WYWIWYG what you write is what you get

#### **PREFACE**

A long, long time ago, in a university not so far away... a battle between synchronous and asynchronous circuit designers raged. The synchronous empire sought to maintain its stronghold over the semiconductor industry as the only way to design large-scale integrated digital systems. However, a band of rebel asynchronous designers have been holding out at a secret base, evading authorities, and plotting to launch an assault on the empire.

Part of the divide between the two parties is attributed to commercial design tool vendors' unwillingness and inability to support the rebel cause. They see no profit in supporting the rebels, as the rebels cannot muster enough demand for special arms (asynchronous tools). And yet much of the rebels disadvantage remains due to their humbler arsenal of weapons. The rebel struggle is often seen as an insurmountable uphill battle. Clearly, advancement of the rebels' technology must come from within.

This is an over-dramatization of the struggle of asynchronous VLSI, however, this prevailing sentiment is captured by the opening quote in the Introduction. Development of asynchronous design tools can only come from *within* the asynchronous academic community, those who understand its principles.

This dissertation addresses a question of how one goes about designing and optimizing asynchronous circuits. Numerous papers in the literature describe methods for mathematically translating sequential programs to parallel programs, and parallel programs to circuits. But does the theory reflect how circuits are designed in practice? (In theory, yes, but in practice, no.) The problem is simply that there are too many ways of accomplishing the same task, each with its own merits and tradeoffs. There is not only one translation, but many translations possible in synthesizing asynchronous circuits from high-level programs.

What navigates asynchronous designers through the sea of design choices? To some extent it is the limited set of instruments and fundamental principles that exist, but to this day, many large-scale custom asynchronous designs are guided by *experience*, wisdom accumulated from many journeys at sea. Experience comes from past designs and lessons learned with their successes and failures. However, if experience were easy to organize and *express*, there would be more literature on the trials and tribulations of circuit designers (not found in textbooks). (Sure, I'll accept that they might not be exciting to read, and in low demand.) Experience has been difficult to pass on to new engineers.

Future design tools beckon for a way of expressing knowledge beyond the fundamentals, so that the wisdom of the ancient masters would not be lost and unnecessarily re-learned with each passing generation. The expert systems area of artificial intelligence is one such approach where a large knowledge base coupled with an inference engine seeks to solve problems by interactively querying a user. At the crossroads of choosing my dissertation topic, I was considering several aspects of asynchronous circuit design from the high-level concurrent programs to the low-level circuit details. Synthesis, the lowering of abstraction from high-level

programs to circuits, looked like a path well-trodden by my predecessors. Optimizations within low-level netlists, seemed to have less potential for improvement than high-level program rewriting and restructuring. To take an analogy from software development: a *structurally* optimized program can be synthesized (compiled) to potentially better circuits (or machine code).

However, the problem with attempting to statically analyze and restructure programs (like source-to-source compilation), is that the number of transformations available at any step is *unbounded*, and that the benefits of transformations were often non-obvious, input-dependent, or involved some tradeoff. Rather than spend effort on program transformations themselves, another useful contribution would be some infrastructure for analyzing the merits of transformations, as guided by the experience of our predecessors. The ultimate goal was an infrastructure for analyses that would easily extend, as engineers contributed their knowledge. If the seas were marked with more lighthouses and warning beacons, navigation for future pioneers would be much easier. Thus, the work within this dissertation describes a method by which experienced designers can teach their apprentices to spot lights in the horizon and shallow rocks beneath the waters, and a means for apprentices to summon the foresight of those who have sailed before them.

David Fang fang@csl.cornell.edu

## CHAPTER 1 INTRODUCTION

I don't think it is a technical issue, but an infrastructure support problem. It's the chicken-or-egg question all over again: we cannot easily design asynchronous systems because appropriate tools aren't available. And there are no tools, the EDA houses say, because there is no demand for them.

Bernard Cole, August 2002 [9]

Many advantages of asynchronous circuits over their synchronous counterparts have been cited for years: robustness to delay variation, design scalability through modularity, formal verification from concurrent programs, energy efficiency due to event-driven activity in lieu of clocks. Despite these advantages, the absence of the asynchronous VLSI design methodology<sup>1</sup> from mainstream adoption has been largely attributed to the lack of design tools<sup>2</sup>. This dissertation is thus motivated by the ever-growing need for asynchronous VLSI design tools.

This dissertation corroborates the importance of profiling and analyzing program executions in choosing concurrent program transformations for optimization. The behavior of asynchronous circuits is specified using high-level concurrent programs; asynchronous circuits are implementations of concurrent programs. While there exist many methods for synthesizing circuits from programs, optimizations in concurrent programs translate to structurally optimized circuits. The work described herein is a powerful trace analysis framework for aiding the rewriting and refinement (transformation and optimization) of high-level asynchronous circuit specifications, which is an important phase of asynchronous design flows. The purpose of such an analysis framework is twofold: it helps designers make informed decisions at each iteration of refinement, and it paves the way for automatically and efficiently exploring otherwise intractable design spaces of equivalent programs. The strengths of our framework lie in the flexibility and re-usability of analysis primitives and procedures for rapid analysis development, and interactivity which allows users to dynamically adjust queries based on information from earlier analyses.

#### 1.1 Preliminary Background

Before we jump into the design flow of asynchronous circuits, we give a brief overview of how asynchronous circuits work, and why this design methodology is worth pursuing over traditional synchronous design.

<sup>&</sup>lt;sup>1</sup>'Asynchronous' design is synonymous with 'self-timed' design.

<sup>&</sup>lt;sup>2</sup>Other reasons include: skepticism "It will never work," ignorance "It is too difficult," and irrationality "Asynchronous VLSI is the Devil."

#### 1.1.1 What is Asynchronous VLSI?

A synchronous circuit is one whose activity is driven by a global clock. During each clock cycle, circuits evaluate their outputs as logical functions of their inputs. On each clock edge that demarcates each cycle, signals are latched and held for the duration of the next cycle, when they are re-evaluated. Thus a global clock orchestrates evaluation and latching in alternation, causing computed data to march along to a single beat in lock-step.

An asynchronous circuit lacks a global clock altogether. Its activity is driven by communication at its boundaries using local handshakes, which follow signaling protocols that indicate when local activity may safely proceed, and when it is complete. Instead of working in lock-step, computation and communication are entirely event-driven.

One naïve performance metric for a synchronous circuit is its global clock frequency. The clock frequency is limited by the slowest path(s) through logic between registers, known as the *critical path*. Violation of this constraint may result in the circuit operating incorrectly if signals are latched before their evaluation is finished. The challenge of optimizing synchronous circuits is in shortening the critical paths as much as possible, or meeting a target frequency, known as timing closure. Reaching timing closure can be an expensive phase of synchronous design verification because it is intertwined with the physical design phase which determines actual path delays (Section 1.1.2).

Asynchronous circuits are evaluated using their throughput, the average rate at which a unit of work is done, where each iteration may take different amounts of time. Critical paths in asynchronous circuits are more subtly defined: asynchronous performance is only determined by paths that are actually exercised at run-time, as opposed to paths that may be exercised in the synchronous counterparts. This is why asynchronous circuits are said to achieve average-case performance, rather than worst-case performance. For example, in a feed-forward, asynchronous pipeline without conditional paths, the critical path is simply the slowest component because all paths are exercised. In a different scenario, a slow component that is rarely used will have little negative impact on an asynchronous system's overall performance.

#### 1.1.2 Impact of timing on design

To understand where design flows for synchronous and asynchronous circuits differ, we examine the role of timing in both design families. In synchronous design, timing plays a role from the beginning to the end: a specific clock frequency is targeted, and pipelining and register retiming is determined as a result of initial critical path estimation. Static timing analysis (STA) is performed throughout the design process to verify that the global timing constraints can be satisfied. A design that is insufficiently pipelined may fail to meet the target frequency because paths between clocked registers are too long. An overly pipelined design will waste

area and energy on registers, add unnecessary cycles of latency on certain paths, and may complicate register retiming. A timed specification is then synthesized to register transfer logic (RTL), which specifies the logical functions between clocked registers. RTL is synthesized into gate-level netlists, which in turn, beget transistor netlists. Each step of synthesis lowers abstraction and adds detail, providing better estimates (but no guarantee) of the actual path delays. The physical design phase (layout geometry and mask design) further increases timing accuracy with extracted electrical parameters and delays from analog simulation such as spice. Placement and routing of circuits should account for delays introduced by wire length and loading.

Other important provisions in timing validation include (but are not limited to): test pattern coverage to generate input-dependent timing signatures of subcircuits, and false path elimination to exclude impossible paths from consideration (which might otherwise exacerbate the worst-case delays). Timing constraints are further exacerbated by variability in the fabrication process, degradation, and variations in operating conditions (temperature, supply voltage, and noise), requiring designers to accommodate additional timing margins. If at any point during synthesis, timing closure is deemed unachievable, then the previous step must be revisited. When a timing constraint is not met during operation (through design error or external cause), some internal signal may be mis-evaluated, potentially causing a visibly wrong result or other silent malfunction. In spite of these challenges with synchronous design, there exist a long legacy of synchronous design tools (and immense labor and capital investments) in the industry to sustain and support the incumbent design methodology for future generations.

Asynchronous circuits liberate designers from having to continually mind the clock. The fact that asynchronous circuits can work correctly with arbitrary, finite gate delays<sup>3</sup> decouples functional correctness from performance optimization. One nice consequence of this separability is that a large class of asynchronous designs<sup>4</sup> can alter the physical pipelining (to improve performance) without affecting the logical pipelining (correctness). The role that timing plays in asynchronous designs is in performance optimization. Asynchronous design families that do utilize timing constraints, however, only do so locally in handshakes and communicating processes without imposing upon any global constraints.

Removing timing constraints from the correctness equation makes it possible to formally verify successive refinements of concurrent programs; each applied transformation is *mathematically proven* to be semantic-preserving. The ability to prove correctness of refinements pays off in an undeniable reduction in design time and effort, as demonstrated by small academic teams producing complex asynchronous chips working in first silicon [19, 20, 46, 47]. Verifiability and a short design time should not be undervalued, especially with the growing size and complexity of integrated circuits!

<sup>&</sup>lt;sup>3</sup>the quasi-delay insensitive (QDI) family

<sup>&</sup>lt;sup>4</sup>slack-elastic designs[42]

The ability to rewrite provably correct concurrent program specifications throughout the design flow is paramount to asynchronous circuit design practice. Asynchronous circuit synthesis can benefit from work in the field of compilers: program rewriting is one form of source-to-source translation, and circuit synthesis is the result of abstraction lowering. Our work described here aims to assist the program rewriting process, be it manual or automated. To recapitulate, the absence of timing from the formulation of correctness in asynchronous circuits has far-reaching implications on its design flow. In the next section, we describe our concept of an asynchronous synthesis flow.

#### 1.2 Asynchronous Design Flow

Both synchronous and asynchronous designs take high-level inputs and eventually produce low-level circuit netlists. Synchronous designs start with high-level behavioral descriptions in a language such as Verilog or VHDL. The initial description is eventually synthesized into RTL and then a circuit netlist, at which point it is handed off for physical design (always minding the timing constraints).

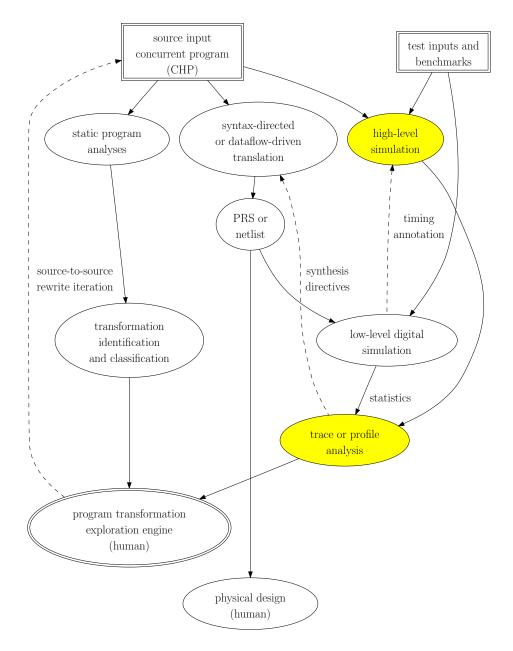

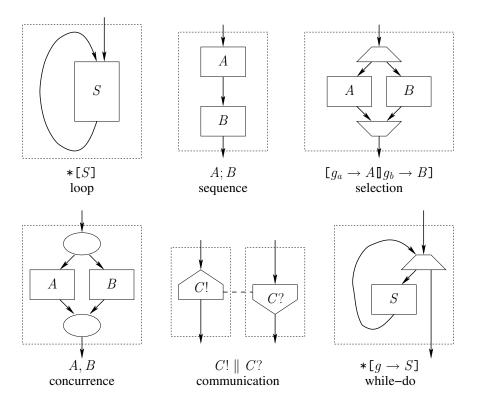

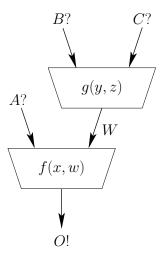

Most existing and proposed asynchronous design tools follow a flow that takes some variant of CSP as input and eventually produces a netlist of circuits. Figure 1.1 is our own rendition of a typical asynchronous synthesis flow diagram. Our asynchronous flow (not unique) begins with a high-level functional description in CHP, a variant of Hoare's CSP [25]. CSP and CHP feature semantics for explicit sequencing, message-passing, flow control, and concurrency. Appendix A provides a quick reference to CHP notation and semantics.

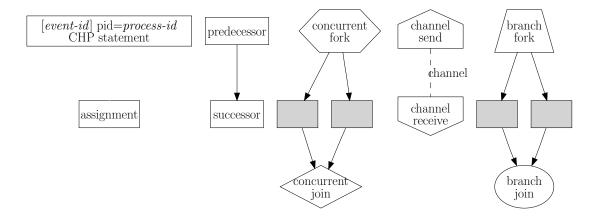

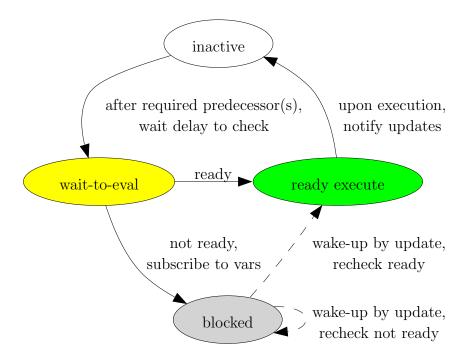

Early pioneering work in asynchronous VLSI showed that asynchronous circuits could be systematically synthesized from an abstract specification in CSP [44]. Syntax-directed translation (SDT) is a method of synthesis where the syntactic constructs map directly into asynchronous circuits that implement the primitive semantics [5]. With SDT, the quality of the resulting circuits depends on the characteristics of the source program; a program written sequentially will produce sequentially operating circuits. Section 2.3.1 discusses conventional techniques for synthesizing asynchronous circuits from high-level concurrent programs: dataflow-driven translation, template-based translation [6, 12, 68, 77]. Dataflow techniques succeed at decomposing larger blocks of code into a set of primitive nodes. Template-based translation is suitable for pattern-matching against sets of known constructs and their corresponding circuits. While synthesizing circuits from programs using any of these techniques produces correct circuits, the resulting circuits are unlikely to be optimized because the input programs may lack explicit parallelism. Concurrency is attained by rewriting the source program explicitly into parallel, communicating processes. In theory, such rewriting can be done automatically with the aid of a source-to-source compiler using static program analysis. In practice, rewriting is often done by hand.

Since the quality of circuits produced by a direct translation depends strongly

Figure 1.1: Asynchronous circuit synthesis flow

on the input (of which there may exist numerous equivalent versions), it behooves a designer to optimize the input of the synthesis phase. Without proper analysis tools, a designer often relies on experience when evaluating the consequence of each high-level, structural transformation. Figure 1.1 emphasizes the use of *feedback* between various phases of synthesis<sup>5</sup>, represented by dashed edges. For example, back-annotating timing from lower level simulations to higher level simulations

<sup>&</sup>lt;sup>5</sup>By 'synthesis', we mean lowering the of level of abstraction while increasing the level of detail of specification.

improves the accuracy (while retaining high-level simulation efficiency) and aids in timing verification [33]. Providing feedback directives (say, derived from profiling) to the circuit translation phase may result in better choices in circuit optimizations. However, the impact of such optimizations cannot compete with the potential available from restructuring the concurrency and control flow of the circuit. Our primary goal is to aid rewriting high-level, concurrent program specifications of asynchronous circuits. Transformations applied to the source program should be justified by the expected benefits on a given set of inputs.

The other inputs to the design flow are test workloads or benchmarks. The test inputs should reflect typical conditions and data that the circuit is expected to encounter; for optimization purposes, they serve as a training set. Either highlevel or low-level (post-synthesis) simulations can be used for comparison. For the work described in this dissertation, we use a high-level simulation of concurrent programs to assess each program's potential to produce optimized asynchronous circuits (Section 3.2). A high-level simulation allows one to evaluate the merits of the *structure* of a concurrent program without assuming details of how the resulting circuits will be synthesized. Program analysis and transformation at a high level is agnostic with respect to the specific asynchronous circuit family used in synthesis, and is thus, widely applicable to all asynchronous circuits design flows. The simulation and analysis framework we present is geared towards assisting rewriting and high-level optimization of concurrent programs.

#### 1.3 Challenge and Contributions

There's more than one way to do it.

Perl motto and philosophy

"I used to write in Perl a lot. Nowadays Perl scares me. It looks like an explosion in an ASCII factory."

> Diederik van der Boor, dot.kde.org, 2007-07-04 (and many others before him)

The major challenge of rewriting or restructuring programs is that the space of functionally equivalent programs is unbounded; it is impossible to consider all equivalent versions of a program, simply because there are infinitely many "obviously poor" legal transformations. Compiler writers realized long ago that aggressive optimization is an iterative process. To know where one should spend effort on optimization and detailed analysis, one should concentrate on the most frequent paths and the most critical paths as found by (simulated) execution. Hotspots and critical paths indicate where transformations are likely to have the greatest impact, and can be used to prioritize program rewriting iterations.

Apart from the obviously good and bad transformations, the benefit of a transformation often depends on the local context in question, and moreover, the inputs and circumstances under which a piece of a program is executed. Chapter 4 gives many examples of transformations whose benefit depends on run-time conditions, not deducible from any static analysis. Many candidate transformations exhibit a tradeoff between metrics such as performance, energy, and area. The designer (or source-to-source compiler) has the daunting task of choosing which transformations to apply. Simulation feedback and profiling will ultimately justify these decisions. Coupling static program analyses with run-time profile analyses increases the potential to effectively and aggressively restructure high-level programs and apply low-level synthesis optimizations [34]. The job of our analysis infrastructure is to make program evaluation more accessible, informative, and flexible to users.

Our contribution to the asynchronous circuit design community is a high-level simulation trace analysis framework, intended to help designers make informed structural optimizations of asynchronous systems, especially where optimization is non-obvious. Our overall infrastructure includes a concurrent program compiler for the CHP language, and an event-driven simulator, from which traces can be produced for detailed run-time analysis. The analysis framework provides an interface for viewing and mining trace information useful to the designer, and complements static program analysis for choosing program transformations. This dissertation describes in detail the analysis primitives and procedures available to the user, and demonstrates how useful analyses are constructed within the framework. We describe several cases of design choices where run-time analyses reveal strengths and weaknesses (not statically inferable) that can be exploited for program optimization.

#### 1.4 Outline

There is much room for development and improvement of asynchronous circuit design tools. The design flow we propose touts program rewriting as having an important role in design: gradually refining the concurrent program so that circuits produced by direct synthesis methods will be *structurally optimized* with respect to a given set of workloads. Program rewriting is orthogonal to all other phases of asynchronous circuit synthesis. The difficult problem of evaluating rewritten programs is aided by our new simulation trace analysis framework, which provides the means to extract detailed performance feedback from any execution. This dissertation describes the analysis framework and demonstrates its benefits.

In Chapter 2, we discuss related work in asynchronous VLSI that precedes our own, covering parallel program evaluation and existing asynchronous design tools. Chapter 3 describes our high-level simulation and trace analysis infrastructure, and justifies our approach. Chapter 4 describes how analyses can be constructed to assess the merits of other concurrent program transformations. In Chapter 5, we present some case studies that further demonstrate the utility of our analysis

framework. Chapter 6 concludes this dissertation.

### CHAPTER 2 BACKGROUND: RELATED WORK

The work for this dissertation spans several fields: parallel programming, performance analysis, asynchronous circuit synthesis. We start with a brief overview of parallel programs and their relation to asynchronous circuit design. The majority of our work builds upon ideas from performance evaluation of software parallel programs. Lastly, we summarize the current state of existing asynchronous circuit synthesis tools, and some of their attempts to incorporate performance profiling.

#### 2.1 Concurrent Programming Languages

Parallel programming has roots in both the software community and in hardware design. Digital circuit design could be construed as one form of parallel programming: synchronous circuits change state at the beat of a global clock as determined by the logic between clocked latches, while asynchronous circuits compute and communicate in an event-driven manner using local handshakes on channels. Explicitly expressing concurrency is very befitting for hardware descriptions languages.

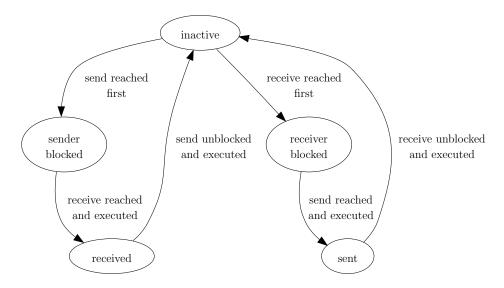

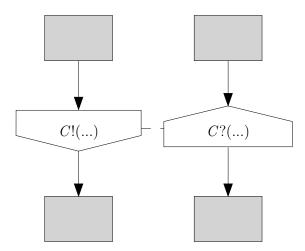

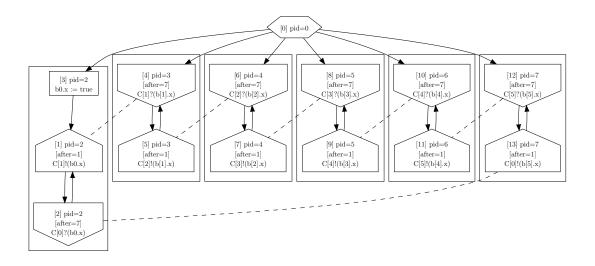

Hoare's Communicating Sequential Processes (CSP) is one such language for expressing concurrency and communication [25, 26]. In CSP, processes communicate data by passing messages over channels; send-receive action pairs (over the same channel) are synchronized point-to-point, i.e. when one of them is reached, it waits until its counterpart (possibly in another process) is reached before both sides proceed. (Send and receive actions are *atomic* and *blocking*.) Communicating Hardware Processes (CHP), a close variant of CSP, was used by Martin to compile parallel programs into delay-insensitive circuits [44, 45]. A quick summary of CHP can be found in Appendix A. We mention other synthesis methods in Section 2.3.

Other languages used for asynchronous circuit specification and synthesis share essentially the same semantics as CSP, dressed in different syntaxes. Variants of CSP provide additional constructs that make concurrent hardware descriptions more convenient or more expressive. Tangram [73] and Balsa Synthesis Tools [12] are similar to each other; the latter is a publicly available variant of the former, which is proprietary. Balsa contains some flow control constructs that are not in CHP, (e.g. sequential if-else) but can be expressed (perhaps less conveniently) using CHP primitives. We have extended our own implementation of CHP with syntactic loop-expansions of repetitive constructs for convenience. TAST, from TIMA, features its own CSP variant (not publicly available) [60]. Haste is the CSP variant used by Handshake Solutions [55]. Occam adds the abstraction of dynamic process lifetime, with process instantiation and termination, which is suitable for abstraction in parallel software [69]. The abstraction of process lifetime may be useful for dynamically reconfigurable hardware, such as asynchronous FPGAs (AFPGA).

The purpose of these languages is to specify the high-level behavior of the asynchronous circuits to be synthesized, without getting involved in the implementation details such as channel encodings and handshake protocols. We use CHP as the high-level language in our design flow because it is simple, and has

worked sufficiently well in the past. The choice of language is not pivotal to our analysis infrastructure; the key concepts in our simulation analysis framework are applicable to any CSP-like language.

#### 2.2 Performance Evaluation of Parallel Programs

Analysis of parallel programs and hardware share a common purpose: to identify performance bottlenecks. Many techniques for performance evaluation of parallel programs inspire similar approaches to evaluating parallel hardware. The following attributes of parallel performance analysis systems are usually desired [21]:

- abstraction The ability to reason about events at a higher level given lowlevel details of execution helps users comprehend large volumes of information more easily.

- 2. **transparency** The ability to measure a system without perturbing the measurement itself is valuable for accuracy.

- 3. **interactivity** The ability to adapt and modify analyses based on observations enables users to iteratively and efficiently experiment with different solutions.

- 4. **portability** Techniques should not be constrained to a particular model or implementation. Since there are different concurrent programming languages, analysis tools that support different languages variants would be more valuable than those limited to only one language.

#### 2.2.1 Measurement and Tracing

Next, we explain how these traits have manifested in parallel software analysis, and how some of the same techniques carry over to hardware analysis.

Instrumentation and sampling. There are several ways of benchmarking parallel programs beyond just measuring execution time. By instrumenting a program with measurement code (in source or binary image), one can generate partial traces of detailed measurements for online or offline analysis. Since instrumentation often perturbs and prolongs the timing of program execution, it comes at the expense of measurement transparency. The convenience of instrumentation comes at the cost of accuracy, depending on the invasiveness of modification. The Paradyn performance analysis tool reduces measurement perturbation and the volume of traced data by dynamically instrumenting the executing program and non-invasively sampling counters updated by the instrumented code [48, 50]. Pablo is an earlier portable and scalable analysis environment capable of dynamically adjusting the level of instrumentation using counter thresholds for feedback [58]. The pC++ performance analysis environment featured both runtime analysis and

offline trace-based profiling [40]. More computationally expensive work was typically reserved for offline evaluation. A benefit of dynamic instrumentation is that queries can be constructed and deployed at run time, enabling dynamic experimentation and refinement of measurements. Periodically sampling measurements of a running program can be less intrusive than instrumentation, but may overlook details that are key to the understanding performance problems [24, 51, 52]. The 'state' of parallel hardware is not representable as call-stacks, but rather, a distributed set of program points. Thus, the stack-sampling approach taken by the gprof sequential program profiler does not fit the concurrent hardware model [22].

**Simulation tracing.** Simulating an executing parallel program, however, essentially decouples measurement from execution. Simulation affords the ability to trace every event in detail without perturbing the simulated execution (transparency), at the cost of trace storage. Alternate approaches trace only what is required to perform the desired analyses [29]. However, one does not always know a priori what information should be exacted before a program is executed; observations can inspire new avenues of investigation [21]. Trace storage in our design flow is justified by the potential need for fine-grain details of execution. In our analysis infrastructure, all analyses and refinements are performed offline on saved traces. A full trace is re-usable across many analyses on the same run; a new trace is required only when the input program or the workload changes. The storage cost and file access performance overhead of tracing can be a drawback when only the simplest queries are desired. For example, lightweight, on-the-fly counters instrumented directly into the simulation to mitigate the need to write and read a trace file. The flexibility of tracing and offline trace analysis is appealing when the analyses demanded are more diverse, detailed, and complex.

Simulation replay. Another benefit of storing a full trace is that it enables efficiently replay of the simulation, potentially revealing details that are not recorded in the trace file. Seeking to arbitrary times in the execution history can be accelerated with incremental checkpoints embedded in the trace file. Full tracing is especially useful for animated visualization of event activity for debugging and evaluation [21].

Version database. Over the course of concurrent program design and evolution, a designer is likely to amass a large history of data for every set of analyses run on each revision and input set. In addition to instrumentation and measurement, SCALEA features a database for storing results of experiments from measuring various versions of a parallel program [72]. Maintaining a database of analysis summaries would be very useful for a design space exploration engine to compare across versions of refinements of a parallel program. We mention the use of databases because they would complement any analysis and measurement framework for an iterative design process.

The ability to obtain measurements from a simulation (as opposed to invasive instrumentation or sampling) gives us the freedom of performing arbitrarily

detailed analyses on execution traces, at the cost of trace storage. Our analysis infrastructure relies heavily on the simulation aspect of our design flow.

#### 2.2.2 Program Simulation

We briefly mention a few simulation environments from which we draw principles for our own simulator. OCCARM is an Occam simulation model of the Amulet1 asynchronous ARM processor [69, 70]. The OCCARM simulation environment featured a monitoring process for collect profile information: occupancy, utilization, throughput, and other internal process state. Measurements are taken according to models of the concurrent processes and explicitly communicated to the monitoring processes. Rather than pass information to a monitor process, our simulator logs every atomic event and state change to a trace file as it executes.

EDPEPPS<sup>1</sup> is a design environment for portable parallel applications that featured a message-passing virtual machine simulator. The full-system simulator is organized in layers, spanning the hardware, operating system, message-passing layer, and running applications [11]. Since we target only circuit design, our discrete event simulator models only hardware. EDPEPPS includes numerous simulation, trace-analysis, and visualization modules, and is easily extensible and integrated with other tools and compilers. Our long term goal is to use our trace analysis framework to drive high-level program transformations in feedback-directed compiler optimizations. Eventually, support for mixed-mode simulation would allow one to map circuit-level events back up to a higher-level constructs.

We describe our simulator further in Section 3.2.

#### 2.2.3 Trace Analysis

There are several existing tools for analyzing traces of parallel programs offline. One of the goals of our trace analysis framework is to provide an interface from which analysis libraries can be easily developed. Medea is one tool for processing trace files produced by monitors during the execution of parallel programs [8]. Medea provides a collection of statistical and numerical analysis modules, which are easy to integrate and coordinate with other tools. Their analysis of trace files is aimed at constructing numerical models of performance as a function of input parameters, for performance prediction. IPS-2 also features a rich library of trace analyses [27, 49].

A proper interface is important for any trace analysis tool. Analysis tools often feature their own interface language to operate on traces or databases of experimental data [4, 63, 76]. Model-driven analysis systems use separate input languages to formulate analyses and queries at a *high level*, while a compiler automatically emits low-level instrumentation and analysis code [29]. We use Scheme as our interface

<sup>&</sup>lt;sup>1</sup>Environment for the Design and Performance Evaluation of Portable Parallel Software

language and provide an API consisting of primitive operations and predicates, thus leveraging all of the capabilities and functionality of the host language (Section 3.3). A layered approach decouples the details of the trace file format from the implementation of the analysis library, leading to better portability.

#### 2.2.4 Temporal Analysis

A large class of trace analyses examine the properties of a program over time (temporal analysis). Properties can vary from simple (e.g. value of a variable) to complex (e.g. comparing activity factor between processes). The entire history of a trace can be classified according to such properties. A summary of time spent in each category or state is called a *time histogram*.

The Occam debugging environment described by Goldszmidt supported checking of temporal logic assertions on a program's execution history, suitable for debugging parallel programs [21]. The IPS-2 tools were capable of accumulating user-specified time histograms computed on traces [49]. The ability to construct arbitrary complex time histograms and queries is valuable for tailoring analyses to specific applications. Our trace analysis framework supports evaluation of arbitrary functions that sweep over traces for temporal analysis (Section 3.3).

Complex probe functions (run over a trace) can be formulated for debugging, performance and activity analysis. For example, one can approximate the dynamic activity factor by sweeping over all events with a fixed-size time window. One can verify the exclusiveness between two processes by 'monitoring' the state of the processes. Temporal analysis is the basis for detecting *phase changes* in programs. It is often desirable to partition the trace of a parallel program into distinct phases, and analyze or optimize each phase separately. Since the notion of phase can be very application-specific, it is important that users be able to apply custom functions to catch phase boundaries. Phase detection functions can be formulated by matching low-level activity patterns that translate to some high-level behavior [59].

#### 2.2.5 Expert Systems Approaches

Expert systems is a field of artificial intelligence that utilizes some subject-specific knowledge of human experts in a knowledge base. The *inference engine* uses the *knowledge base* to present a series of questions to the user in an attempt to determine an answer in the subject domain. Some common examples of expert systems are found in technical troubleshooting and medical diagnosis. While we do not employ expert systems techniques in our framework, we adopt the concept of being able to extend a knowledge base of analyses and diagnostics for performance optimization.

Parallel programming and circuit design are domains where *experience* often helps with problem solving and diagnosis. Merlin is a tool for automating parallel program performance analysis that employs a knowledge base of rules that map

performance symptoms to possible causes, and causes to possible solutions [34]. As a designer's experience grows, the knowledge base can be appended with new expertise in performance diagnosis, making Merlin useful to non-expert parallel programmers. KAPPA-PI organizes its knowledge base into a hierarchy of possible performance bottlenecks from general rules down to specific rules [15, 16]. For example, a "frequently blocked sender" is a subclass of general "communication issues," and "barrier wait imbalance" can be a subclass of general structural problems. Typical analysis sessions start with the same core set of diagnostics, followed by different refined diagnostics with each iteration.

With our analysis infrastructure, one can construct an expert system for performance diagnosis by building a knowledge base of rules for diagnostics that trigger refined analyses and queries, which invoke routines from an analysis library.

#### 2.2.6 User Interface Design

For analysis tools to be accessible to non-experts, it is essential to be able to present information in a structured (and often graphical) manner. Nearly every mentioned tool for performance analysis of parallel programs touts some graphical user interface and visualizations of analyses. Guidelines for effective interface design have been described in [54]. Although we have not developed any beautiful graphics along with our infrastructure, we do make information easily available to data visualization tools to leverage our work and others' work.

#### 2.3 Asynchronous Synthesis Tools

Our review of other asynchronous circuit synthesis tools covers two aspects: methods for synthesizing circuits (lowering abstraction level from concurrent programs), and existing integrated design flows.

#### 2.3.1 Circuit synthesis methods

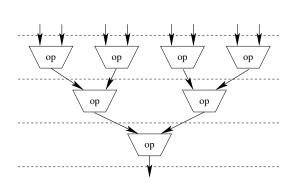

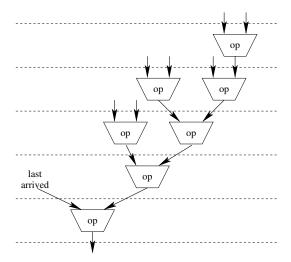

Our work does not focus on circuit synthesis; however, understanding various approaches to synthesis gives some insight on how the results obtained from high-level trace analyses can direct better synthesis, and how high-level transformations may improve the results of synthesis. Syntax-directed translation (SDT) was the first approach used to synthesize asynchronous circuits from high-level concurrent program descriptions [6, 44, 45]. With SDT, syntactic constructs (such as sequence, concurrency, communication, and selection) are recursively mapped to circuits that implement these primitives. However, without fine-grain process decomposition, the resulting circuits would exhibit only as much concurrency as was explicitly written. *Projection* was introduced to partition variable assignments into send-receive pairs to facilitate process decomposition [41]. Process decomposition results in smaller and simpler processes capable of achieving greater throughput.

Once concurrent processes are factored into primitive processes, they can be handed off to circuit synthesizers. A. Lines described a method for synthesizing pipelined quasi-delay insensitive (QDI) circuits using known templates for common four-phase handshake protocols [38]. By changing relatively few subcircuits to implement different functions, a designer can easily write netlists, even by hand. The circuit templates can be chosen based on size, latency, throughput, energy, and scalability. This method of synthesis is typically reserved for the leaf cells of finely decomposed concurrent processes. Since there can be more than one way to synthesize circuits, this translation step can be guided by hints from both high-level and low-level performance profiling. For example, a non-critical path may favor smaller circuits for saving area without compromising performance.

Petri Nets (PN) are also commonly used to describe handshaking protocols and for synthesizing asynchronous circuits with tools such as Petrify [10, 35, 36, 37]. Since there are several handshaking protocols to choose from and multiple correct implementations for each protocol, run-time profiling of the high-level program can help the above synthesis methods decide which implementation is more suitable, depending on path criticality.

The ACK synthesis tool (no longer maintained) targeted synthesis of datapaths with (one or more) separate controllers from high-level descriptions, initially in Verilog or VHDL [31]. The controls for the datapath are synthesized as asynchronous state machines, using control graph partitioning to simplify synthesis. The computation portion of the datapath leverages standard synchronous (VHDL) back-end synthesis. The TiDE tools translate Haste program descriptions into bundled-data style circuits with a 4-phase control handshake, which requires separate timing validation of delay elements [64]. The leaf circuits are mapped to a standard cell library, chosen by the user, using standard EDA tools. The "different where needed, standard where possible" mantra, where existing synchronous tool flows are used to a great extent, is prevalent among several asynchronous synthesis tool chains — circuit synthesis may not be optimal, but they provide a short path<sup>2</sup> to a working design flow.

Message-passing concurrent languages fit extremely well with the conventional dataflow framework in optimizing compilers. Data-driven (or dataflow-driven) synthesis is another approach that produces circuits in a manner purely dependent on data dependencies [68, 77]. Data-driven synthesis produces finely decomposed and deeply pipelined processes, sometimes overly pipelined on latency-critical paths. One proposed solution was to apply sequential and parallel clustering algorithms to un-pipeline selected processes [78]. Clustering is also applicable to FPGA-style synthesis, where a computation is mapped onto a logic fabric with fixed resources [56]. Where static analysis runs into limitations, clustering heuristics would benefit from guidance based on profile analyses of simulated executions.

<sup>&</sup>lt;sup>2</sup>low development cost, time, and effort

#### 2.3.2 Existing tool flows

The methods described above have been harnessed in tools developed in academia and industry. We summarize the simulation and analysis capabilities of some of those tools.

The Balsa Synthesis Tools, based on Tangram, follow template-based, syntax-directed synthesis, and provide a library of primitive components [12, 73]. Balsa includes a simulator that produces a trace of channel and process activity for profiling [13]. Balsa provides a variety of visualizations to aid in debugging and analysis, such as deadlock causes. The Balsa designers realized the importance of being able to iteratively refine a source description of a concurrent program to optimize the circuits produced by syntax-directed translation [32]. However, the provided analyses are very rudimentary and not easily extensible<sup>3</sup>, and there is little headway towards assisting program rewriting using the existing analyses.

Profiling simulation of asynchronous circuits already exists in synthesis tools. The TIMA Asynchronous Synthesis Tool (TAST) includes an activity profiler capable of collecting frequency statistics about execution paths and channel/variable data [60]. The activity profile acquired using TAST or similar tools is intended to guide optimizations:

- Area and energy can be reduced by eliminating unused circuits, or downsizing infrequently used circuits.

- Performance may be improved by scheduling more aggressively on frequent critical paths.