## WIDTH-ADAPTIVE AND NON-UNIFORM ACCESS ASYNCHRONOUS REGISTER FILES

A Thesis

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Master of Science

by

David Fang January 2004 © 2004 David Fang ALL RIGHTS RESERVED

#### ABSTRACT

At the heart of practically every modern microprocessor core sits some form of register file, whose purpose is to hold and supply intermediate results of computations to other computation units. As register files grow in size and in the number of ports to support increasing instruction-level parallelism (ILP), it becomes extremely difficult to meet timing requirements in clocked designs, and the energy consumed by accesses increases significantly. Asynchronous microprocessors share many of the same design issues, however, we have at our disposal a different family of techniques due to the robust and modular nature of self-timed design.

Starting with a sequential specification of a typical asynchronous register file, we decompose the specification into fine-grain parallel processes for the core, bypass and control that implement the specified register file. To improve the throughput of the core, we vertically pipeline the read and write ports into smaller blocks of data, and we describe the locking mechanism that maintains pipelined mutual exclusion among reads and writes. Using standard handshaking expansion templates, we synthesize quasi-delay insensitive production rules that describe the circuits for the pipelined core ports. This initial design serves as the basis for comparison for the transformations presented in the remainder of the thesis.

The key contributions are described in detail throughout the remainder of the thesis. We extend the base design to support a width-adaptive datapath representation, which leads to significant energy reduction by conditionally communicating higher significant bits of integers, with little performance degradation. We show how the bypass can be extended to reduce core accesses with alternative implementations of the hard-wired zero register and bypass-forwarding of duplicate operands using Port Priority Selection. We show the improvement in speed and energy gained by splitting the register core into two banks. As an alternative to banking, which is interconnect-limited, we present the technique of nesting the register core into non-uniform banks without increasing the interconnect requirement to facilitate faster accesses to more frequently used registers and slower accesses to less frequently used registers, and thus, achieve average-case improvement. We have laid out the explored design space of register files in TSMC .18 $\mu m$  technology, and present performance and energy results for all register cores simulated using a variant of spice.

## **Biographical Sketch**

The author graduated from Franklin Regional Senior High School in Murrysville, PA with Honors with Highest Distinction in the class of 1997. He enrolled at the California Institute of Technology in 1997, ambitiously intending to tackle electrical engineering, physics, and a twist of applied mathematics, but only managed to graduate with a Bachelor of Science in Electrical Engineering with Honors in 2001.

The roots of his interest in asynchronous VLSI trace back to the EE/CS181abc class he took as an undergrad, taught by Prof. Alain Martin and his research group members. The author received a National Defense Science and Engineering Graduate Fellowship, sponsored by the Office of Naval Research. Since the summer of 2001, the author has been a student of the Computer Systems Laboratory in the Cornell Electrical and Computer Engineering Department, under the guidance of Prof. Rajit Manohar, a former student of Prof. Martin.

To supplement his background in asynchronous VLSI, the author is minoring in computer science, and maintains interest in computer architecture and compilers, which spans the hardware and software aspects of computer engineering. Aside from being passionate about his work, he also maintains strong interest in music and dance — but only when time permits, of course. dedicated to my dear family and friends, near and far, from whom I've been absent too long

### Acknowledgments

First, I'd like to thank my advisor, Prof. Rajit Manohar, for his continuous guidance, support, and his patience throughout the lifetime of this undertaking. Thanks to my committee members, Profs. Martin Burtscher and Radu Rugina, for taking the time to parse the entire thesis through their pipelines and provide constructive feedback.

The experience of the Master's project would not have been as enjoyable without constant encouragement and a sense of humor from my fellow computer engineers in the Computer Systems Laboratory. It is my pleasure and honor to be in the company of "Asynchronians" John Teifel, Virantha Ekanayake, Clint Kelly, and David Biermann.

A nod goes to an innumerable group of friends who, with some success from time to time, have lured me away from my arduous studies to enjoy life as it should be enjoyed. Without them, I would've lost my wits long ago. (No comical retorts, please!)

Finally, the work for thesis was entirely funded by the National Defense Science and Engineering Graduate Fellowship with sponsorship from the Office of Naval Research.

## **Table of Contents**

| 1        | Intr | oduction                             | 1  |

|----------|------|--------------------------------------|----|

|          | 1.1  | Background                           | 2  |

|          |      | 1.1.1 Asynchronous Circuit Synthesis | 2  |

|          |      | 1.1.2 Register File Models           | 9  |

|          | 1.2  | Overview                             | 10 |

| <b>2</b> | Pro  | cess Specification and Decomposition | 13 |

|          | 2.1  | Sequential Specification             | 14 |

|          | 2.2  | Primary Decomposition                | 17 |

|          | 2.3  | Register Core                        | 22 |

|          | 2.4  | Register Bypass                      | 26 |

|          | 2.5  | Register Control                     | 26 |

|          | 2.6  | Summary                              | 28 |

| 3        | Ver  | tical Pipelining                     | 30 |

|          | 3.1  | Preliminary Concepts                 | 31 |

|          | 3.2  | Related Work                         | 36 |

|          | 3.3  | Pipeline Templates                   | 39 |

|          | 3.4  | Pipelined Bypass                     | 40 |

|          | 3.5  | Pipelined Mutual Exclusion: Core     | 41 |

|          | 3.6  | Register Zero                        | 44 |

|          | 3.7  | Summary                              | 44 |

| 4        | Cor  | e Base Design                        | 46 |

|          | 4.1  | Template Handshaking Expansions      | 46 |

|          |      | 4.1.1 Half-Buffer vs. Full-Buffer    | 49 |

|          |      | 4.1.2 Core Read Port HSE             | 51 |

|          |      | 4.1.3 Core Write Port HSE            | 53 |

|          | 4.2  | Floor Decomposition                  | 55 |

|          |      | 4.2.1 Decomposed Reading             | 55 |

|          |      | 4.2.2 Decomposed Writing             | 62 |

|          | 4.3  | Production Rule Synthesis            | 67 |

|          | -    | 4.3.1 Core Register Cells            | 67 |

|          |      | 4.3.2 Control Propagation            | 69 |

|          |     | 4.3.3 Data Interface Cell                                                                |

|----------|-----|------------------------------------------------------------------------------------------|

|          |     | 4.3.4 Handshake Control                                                                  |

|          |     | 4.3.5 Circuit Variations and Optimizations                                               |

|          | 4.4 | Banking                                                                                  |

|          |     | 4.4.1 Related Work                                                                       |

|          |     | 4.4.2 Core Banking                                                                       |

|          |     | 4.4.3 Bypass Banking                                                                     |

|          |     | 4.4.4 Control Modifications                                                              |

|          | 4.5 | Results                                                                                  |

|          |     | 4.5.1 Reading                                                                            |

|          |     | $4.5.2  \text{Writing}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

|          | 4.6 | Summary                                                                                  |

| <b>5</b> | Wie | th Adaptivity 88                                                                         |

|          | 5.1 | Related Work                                                                             |

|          | 5.2 | WAD Encoding                                                                             |

|          | 5.3 | CHP Transformations                                                                      |

|          |     | 5.3.1 Bypass                                                                             |

|          |     | 5.3.2 Core                                                                               |

|          | 5.4 | Template Handshaking Expansions                                                          |

|          |     | 5.4.1 Core Read Port HSE                                                                 |

|          |     | 5.4.2 Core Write Port HSE                                                                |

|          |     | 5.4.3 HSE Summary                                                                        |

|          | 5.5 | Width-Adaptive Production Rules                                                          |

|          |     | 5.5.1 WAD Control Propagation                                                            |

|          |     | 5.5.2 WAD Read Handshake Control                                                         |

|          |     | 5.5.3 WAD Write Handshake Control                                                        |

|          |     | 5.5.4 PRS Comparison of WAD Write Ports                                                  |

|          | 5.6 | Results                                                                                  |

|          |     | 5.6.1 Area                                                                               |

|          |     | 5.6.2 Reading                                                                            |

|          |     | 5.6.3 Writing, Unconditional Write-Enable                                                |

|          |     | 5.6.4 Writing, Conditional Write-Enable                                                  |

|          | 5.7 | Summary                                                                                  |

| 6        | Reg | gister Zero 116                                                                          |

|          | 6.1 | Related Work                                                                             |

|          | 6.2 | Reading Register Zero                                                                    |

|          |     | 6.2.1 Bypass Modifications                                                               |

|          |     | 6.2.2 Control Modifications                                                              |

|          |     | 6.2.3 Impact of Width-Adaptivity                                                         |

|          | 6.3 | Writing Register Zero                                                                    |

|          | -   | 6.3.1 Control Modifications                                                              |

|          |     | 6.3.2 Impact of Width-Adaptivity                                                         |

|          |     |                                                                                          |

|   | 6.4 | Summ           | ary                                             | <br>• | • | • | . 121 |

|---|-----|----------------|-------------------------------------------------|-------|---|---|-------|

| 7 | Por | t Prior        | rity Selection                                  |       |   |   | 122   |

|   | 7.1 |                | d Work                                          |       |   |   | . 123 |

|   | 7.2 |                | s Modifications                                 |       |   |   |       |

|   | 7.3 | 0 <b>1</b>     | DI Modifications                                |       |   |   |       |

|   | 7.4 |                | ary                                             |       |   |   |       |

|   | -   |                |                                                 |       |   |   |       |

| 8 |     |                | orm Control Completion                          |       |   |   | 128   |

|   | 8.1 | -              | er Statistics                                   |       |   |   |       |

|   | 8.2 |                | ancing Completion Trees                         |       |   |   |       |

|   | 8.3 |                | S                                               |       |   |   |       |

|   |     | 8.3.1          | Non-WAD Reading                                 |       |   |   |       |

|   |     | 8.3.2          | Non-WAD Writing                                 |       |   |   |       |

|   |     | 8.3.3          | WAD Reading                                     |       |   |   |       |

|   |     | 8.3.4          | WAD Writing                                     | <br>• | • | • | . 137 |

|   | 8.4 | Summ           | ary                                             | <br>• | • | • | . 140 |

| 9 | Cor | e Parti        | itioning via Nesting                            |       |   |   | 141   |

| U | 9.1 |                | d Work and Applications                         |       |   |   |       |

|   | 9.2 |                | g CHP Decomposition                             |       |   |   |       |

|   | 5.2 | 9.2.1          | Unconditional Control Propagation               |       |   |   |       |

|   |     | 9.2.1<br>9.2.2 | WAD Control Propagation                         |       |   |   |       |

|   | 9.3 | -              | haking Expansion Modifications                  |       |   |   |       |

|   | 5.0 | 9.3.1          | Unconditional Read Control Propagation          |       |   |   |       |

|   |     | 9.3.1<br>9.3.2 | Unconditional Write Control Propagation         |       |   |   |       |

|   |     | 9.3.2<br>9.3.3 | WAD Read Control Propagation                    |       |   |   |       |

|   |     | 9.3.3<br>9.3.4 |                                                 |       |   |   |       |

|   | 9.4 |                | WAD Write Control Propagation                   |       |   |   |       |

|   | 5.1 | 9.4.1          | Read Data Nesting                               |       |   |   |       |

|   |     | 9.4.2          | Non-WAD Write Data Nesting                      |       |   |   |       |

|   |     | 9.4.2<br>9.4.3 | Non-WAD Read Control Nesting                    |       |   |   |       |

|   |     | 9.4.3<br>9.4.4 | WAD Read Control Nesting                        |       |   |   |       |

|   |     | 9.4.4<br>9.4.5 | 0                                               |       |   |   |       |

|   |     |                | Non-WAD Write Control Nesting                   |       |   |   |       |

|   | 05  | 9.4.6          | WAD Write Control Nesting                       |       |   |   |       |

|   | 9.5 |                |                                                 |       |   |   |       |

|   |     | 9.5.1          | Read Data Nested Interconnect                   |       |   |   |       |

|   |     | 9.5.2          | Write Data Nested Interconnect                  |       |   |   |       |

|   |     | 9.5.3          | Read/Write Nested Data Interface                |       |   |   |       |

|   |     | 9.5.4          | WAD Nested Read Handshake Control               |       |   |   |       |

|   |     | 9.5.5          | Unconditional Read Control Nested Interconnect  |       |   |   |       |

|   |     | 9.5.6          | WAD Read Control Nested Interconnect            |       |   |   |       |

|   |     | 9.5.7          | Unconditional Write Control Nested Interconnect |       |   |   |       |

|   |     | 9.5.8          | WAD Write Control Nested Interconnect           |       | • |   | . 179 |

|    | 9.6 | Results                                                | 0        |

|----|-----|--------------------------------------------------------|----------|

|    |     | 9.6.1 Area                                             | 2        |

|    |     | 9.6.2 Non-WAD Reading                                  | 2        |

|    |     | 9.6.3 Non-WAD Writing                                  | 6        |

|    |     | 9.6.4 WAD Reading                                      | 9        |

|    |     | 9.6.5 WAD Writing, Unconditional Outer Write-Enable 19 | 1        |

|    |     | 9.6.6 WAD Writing, Conditional Outer Write-Enable 19   | 4        |

|    | 9.7 | Summary                                                | 7        |

| 10 | Con | clusion 19                                             | 9        |

| 10 |     | Recapitulation                                         |          |

|    |     | Choice                                                 |          |

|    |     | Future Work         20                                 |          |

|    | a   |                                                        | _        |

| Α  | Sun | nmary of CHP Notation 20                               | 5        |

| В  | Byp | Dass CHP 20                                            |          |

|    | B.1 | Base Design                                            | 7        |

|    | B.2 | Vertically Pipelined                                   | 9        |

|    | B.3 | Width-Adaptive                                         |          |

|    | B.4 | Register Zero                                          |          |

|    | B.5 | Port Priority Select                                   |          |

|    | B.6 | Banking                                                | 3        |

| С  | Con | trol CHP 21                                            | <b>4</b> |

|    | C.1 | Base Design                                            | 4        |

|    | C.2 | Banking                                                |          |

|    | C.3 | Register Zero                                          | 9        |

|    | C.4 | Port Priority Select                                   | 0        |

| D  | Cor | e CHP 22                                               | <b>2</b> |

|    | D.1 | Pipelined Core                                         | 2        |

|    | D.2 | WAD Core                                               |          |

|    | D.3 | Nested Core                                            | 6        |

|    | D.4 | WAD Nested Core                                        | 8        |

| Е  | Cor | e HSE 23                                               | 0        |

| -  | E.1 | Pipelined Core                                         |          |

|    | E.2 | WAD Core                                               |          |

|    | E.3 | Non-WAD Nested Core                                    |          |

|    | -   | WAD Nested Core                                        |          |

|    |     |                                                        |          |

| $\mathbf{F}$ | Partial H  | SEs of the Core                                   | <b>240</b> |

|--------------|------------|---------------------------------------------------|------------|

|              |            | WAD Core                                          |            |

|              | F.2 WAD    | Core                                              |            |

|              | F.2.1      | 8                                                 |            |

|              | F.2.2      |                                                   |            |

|              | F.2.3      | Writing Control, Conditional Write-Enable         |            |

|              |            | WAD Nested Core                                   |            |

|              | F.3.1      | Modified Data Interface                           |            |

|              | F.3.2      | Nested Data Interconnect                          |            |

|              | F.3.3      | Nested Control Interconnect                       |            |

|              |            | Nested Core                                       |            |

|              | F.4.1      | 0                                                 |            |

|              | F.4.2      | Writing                                           | 248        |

| G            | Reset Co   | nvention                                          | <b>249</b> |

| -            |            | al Reset Signals                                  |            |

|              |            | shake Protocol Reset State                        |            |

|              |            |                                                   |            |

| Η            | Core PRS   |                                                   | 254        |

|              | -          | ter Cell Array                                    |            |

|              |            | Nested Interconnect                               |            |

|              |            | col Propagation Array                             |            |

|              |            | rol Nested Interconnect                           |            |

|              |            | Interface Array                                   |            |

|              |            | Handshake Control                                 |            |

|              | Н.6.1      |                                                   |            |

|              | H.6.2      |                                                   |            |

|              | H.6.3      | Nested WAD Read Handshake Control                 |            |

|              |            | e Handshake Control                               |            |

|              | H.7.1      |                                                   |            |

|              |            | WAD Write Handshake Control, Unconditional Enable |            |

|              | H.7.3      |                                                   |            |

|              | H.7.4      | ,                                                 |            |

|              | 11.7.4     |                                                   | 215        |

| Ι            | Mine Eye   | es Have Seen The Glory                            | 274        |

| J            | Tables of  | Results                                           | 275        |

| Bi           | bliography | 7                                                 | 293        |

## List of Tables

| 1.1          | Register file components affected by various transformations $11$                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $4.1 \\ 4.2$ | Layout component dimensions                                                                                                                                         |

| 4.3          | sign register file, for a block size of 4 bits x 32 registers                                                                                                       |

| 4.4          | bank with a block size of 4 bits x 16 registers                                                                                                                     |

|              | sign register file, for a block size of 4 bits x 32 registers                                                                                                       |

| 4.5          | Write-access performance and energy comparisons for a register<br>bank with a block size of 4 bits x 16 registers                                                   |

| 5.1          | The encoding of width-adaptive datapath (WAD) blocks 91                                                                                                             |

| 5.2          | Read-access performance and energy comparisons for the WAD reg-<br>ister file, for a block size of 4 bits x 32 registers                                            |

| 5.3          | Read-access performance and energy comparisons for the WAD reg-<br>ister file, for a block size of 4 bits x 16 registers                                            |

| 5.4          | Write-access performance and energy comparisons for the WAD register file, with the unconditional write-enable variation, for a block size of 4 bits x 32 registers |

| 5.5          | Write-access performance and energy comparisons for the WAD register file, with the unconditional write-enable variation, for a                                     |

| 5.6          | block size of 4 bits x 16 registers                                                                                                                                 |

|              | size of 4 bits x 32 registers                                                                                                                                       |

| 5.7          | Write-access performance and energy comparisons for the WAD register file, with the conditional write-enable variation, for a block size of 4 bits x 16 registers   |

| 8.1          | MIPS register conventions                                                                                                                                           |

| 8.2          | Cumulative dynamic usage frequencies of the 20 most read and written MIPS registers                                                                                 |

| 8.3          | Read-access performance and energy comparisons for the non-uniform<br>non-WAD register file with 16 registers                                                       |

| 8.4        | Write-access performance and energy comparisons for the non-uniform non-WAD register file with 16 registers                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 8.5        | Read-access performance and energy comparisons for the non-uniform<br>WAD register file with 16 registers                                |

| 8.6        | Write-access performance and energy comparisons for the non-uniform WAD (unconditional write-enable) register file with 16 registers 139 |

| 8.7        | Write-access performance and energy comparisons for the non-uniform WAD (conditional write-enable) register file with 16 registers 139   |

| 9.1        | Read-access performance and energy comparisons for the nested register file with 16 registers per partition                              |

| 9.2        | Read-access performance and energy comparisons for the nested<br>register file with 8 registers per partition                            |

| 9.3        | Write-access performance and energy comparisons for the nested<br>register file with 16 registers per partition                          |

| 9.4        | Write-access performance and energy comparisons for the nested<br>register file with 8 registers per partition                           |

| 9.5        | Read-access performance and energy comparisons for the WAD<br>nested register file with 16 registers per partition                       |

| 9.6        | Read-access performance and energy comparisons for the WAD<br>nested register file with 8 registers per partition                        |

| 9.7        | Write-access performance and energy comparisons for the WAD<br>nested register file with 16 registers per partition, unconditional       |

| 9.8        | outer write-enable variation                                                                                                             |

| 5.0        | nested register file with 8 registers per partition, unconditional<br>outer write-enable variation                                       |

| 9.9        | Write-access performance and energy comparisons for the WAD<br>nested register file with 16 registers per partition, conditional outer   |

| 9.10       | write-enable variation                                                                                                                   |

|            | register file with 8 registers per partition, conditional outer write-<br>enable variation                                               |

| J.1        | Data table symbols                                                                                                                       |

| J.2        | All non-WAD read port performance and energy results 277                                                                                 |

| J.3<br>J.4 | All WAD read port performance and energy results                                                                                         |

| J.5        | Impact of width-adaptivity on half-buffer read port performance<br>and energy                                                            |

| J.6        | Impact of width-adaptivity on full-buffer read port performance<br>and energy                                                            |

| J.7<br>J.8 | Impact of bank size on read port performance and energy                                                                                  |

| 0.0        | $\frac{1}{2}$                                                                                                                            |

| J.9  | Impact of nesting on read latency                                             |

|------|-------------------------------------------------------------------------------|

| J.10 | Impact of extending a bank with nesting on read port performance              |

|      | and energy                                                                    |

| J.11 | Impact of non-uniform accesses on read port performance and energy283         |

| J.12 | All non-WAD write port performance and energy results 284                     |

| J.13 | All WAD-uwen write port performance and energy results 285                    |

| J.14 | All WAD-cwen write port performance and energy results 286                    |

| J.15 | Impact of chosen buffering on write port performance and energy $% 287$       |

| J.16 | Impact of width-adaptivity on half-buffer write port performance              |

|      | and energy                                                                    |

| J.17 | Impact of width-adaptivity on full-buffer write port performance              |

|      | and energy                                                                    |

| J.18 | Impact of bank size on write port performance and energy 290 $$               |

| J.19 | Impact of bank size on write latency                                          |

| J.20 | Impact of nesting on write latency                                            |

| J.21 | Impact of extending a bank with nesting on write port performance             |

|      | and energy                                                                    |

| J.22 | Impact of non-uniform accesses on write port performance and energy<br>292 $$ |

|      |                                                                               |

# List of Figures

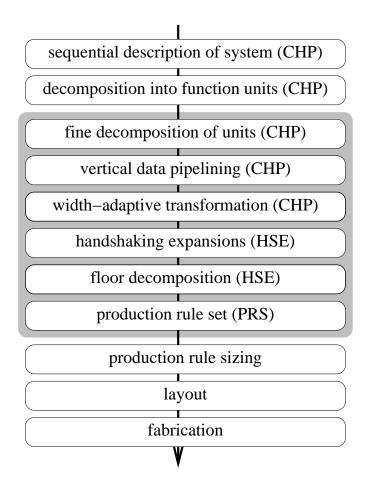

| 1.1  | Flow diagram of QDI synthesis                                                            | 5  |

|------|------------------------------------------------------------------------------------------|----|

| 1.2  | Precharge half-buffer (PCHB) with active-low acknowledgments                             | 7  |

| 1.3  | Two equivalent implementations of a precharge full-buffer (PCFB)                         |    |

|      | with active-low acknowledgments                                                          | 7  |

| 1.4  | Abstract PCHB circuit template for a function with $n$ inputs and                        |    |

|      | m output channels                                                                        | 8  |

|      | -                                                                                        |    |

| 2.1  | Register file's channel interface with its environment                                   | 14 |

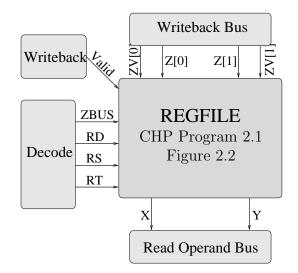

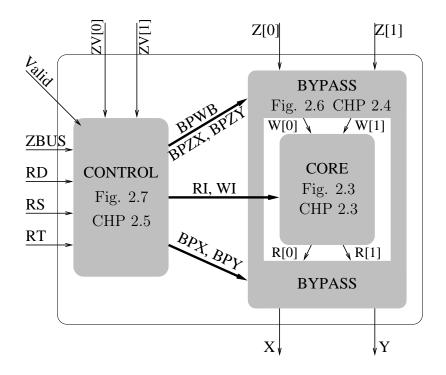

| 2.2  | Schematic of the Register File process decomposition                                     | 18 |

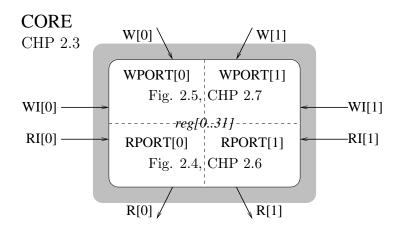

| 2.3  | Schematic of the $CORE$ decomposition $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 22 |

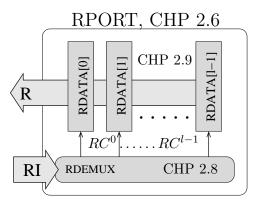

| 2.4  | Schematic of read port                                                                   | 23 |

| 2.5  | Schematic of write port                                                                  | 23 |

| 2.6  | Schematic of the bypass decomposition                                                    | 27 |

| 2.7  | Schematic of the control decomposition                                                   | 29 |

| 3.1  | Vertically pipelined core array                                                          | 33 |

| 3.2  | Synchronous or asynchronous block-aligned datapath communication                         | 33 |

| 3.3  | Synchronous parallel skewed vertical pipeline operation                                  | 34 |

| 3.4  | Snapshot of vertically pipelined, block-skewed datapath communi-                         |    |

| 0 5  |                                                                                          | 35 |

| 3.5  | Schematic of pipelined core reading and writing blocks                                   | 41 |

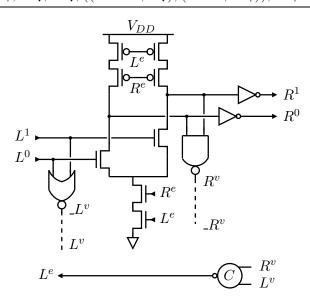

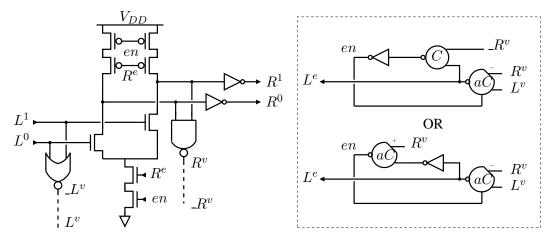

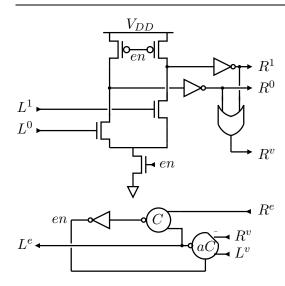

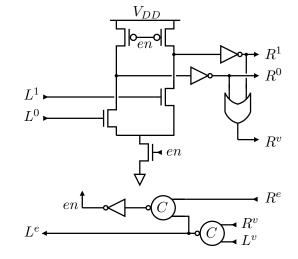

| 4.1  | Precharge enable-valid full-buffer (PCEVFB) template                                     | 49 |

| 4.2  | Precharge enable-valid half-buffer (PCEVHB) template                                     | 49 |

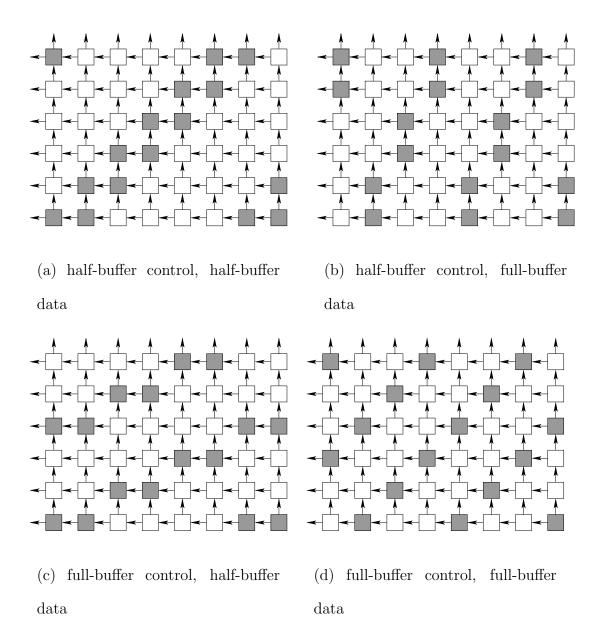

| 4.3  | Examples of two-dimensional pipelining                                                   | 50 |

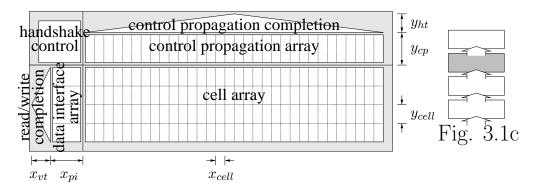

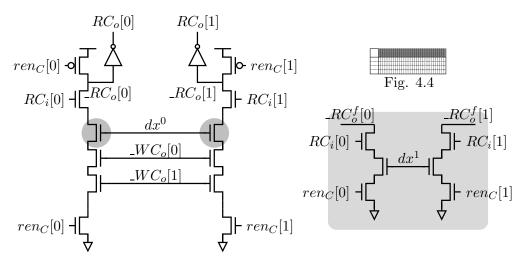

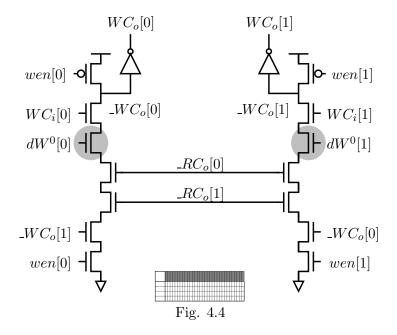

| 4.4  | Floorplan of a vertically pipelined register core block for reading                      |    |

|      | and writing                                                                              | 56 |

| 4.5  | Floor decomposition of a read port block, shown with channel sig-                        |    |

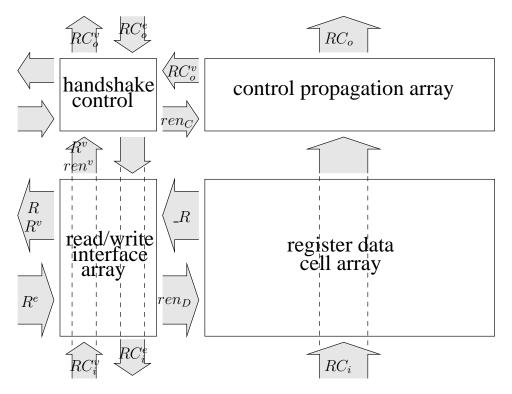

|      | nals and some internal signals at component boundaries                                   | 56 |

| 4.6  | Floor decomposition of a PCEVFB read port                                                | 57 |

| 4.7  | Floor decomposition of a PCEVHB read port                                                | 57 |

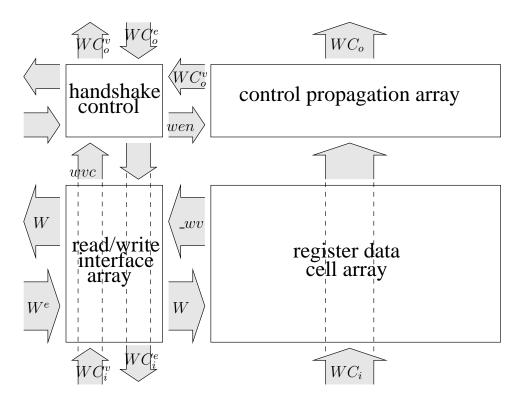

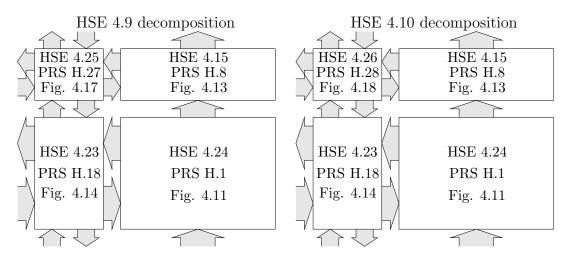

| 4.8  | Floor decomposition of a write port block, shown with channel                            |    |

|      | signals and some internal signals at component boundaries                                | 63 |

| 4.9  | Floor decomposition of a PCEVFB write port                                               | 63 |

| 4.10 | Floor decomposition of a PCEVHB write port                                               | 63 |

|      |                                                                                          |    |

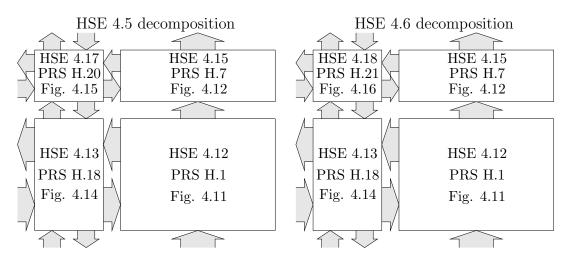

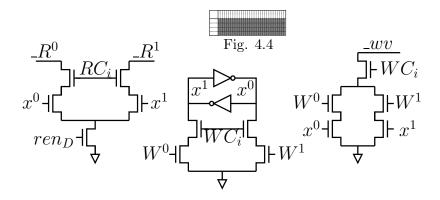

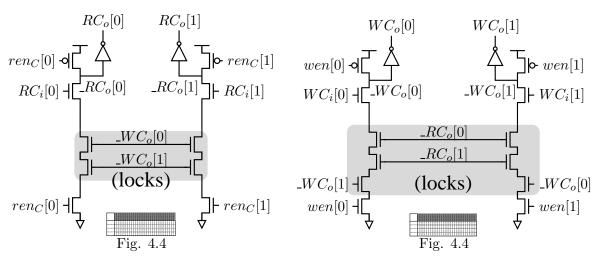

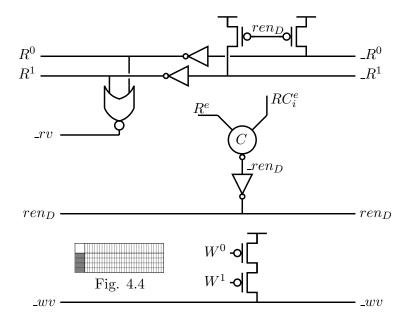

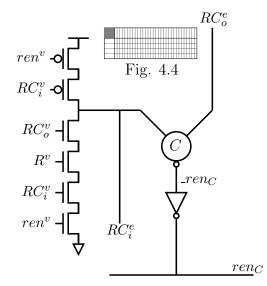

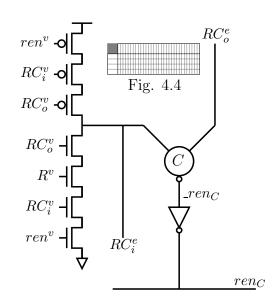

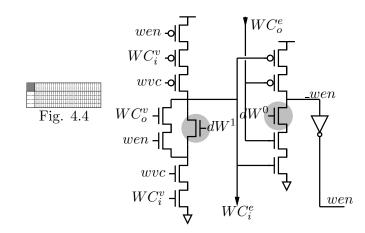

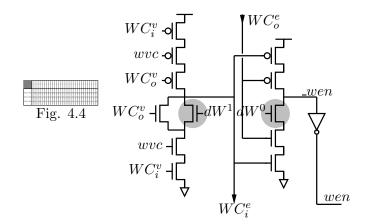

| 4.11         | QDI Register core cell. Only one read and one write port are shown.             | 68       |

|--------------|---------------------------------------------------------------------------------|----------|

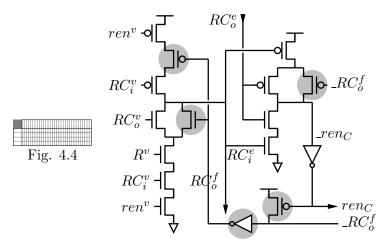

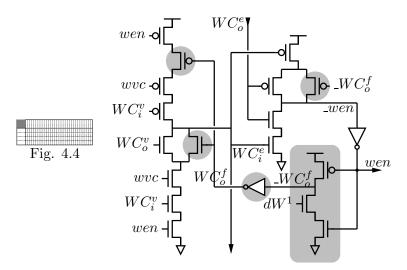

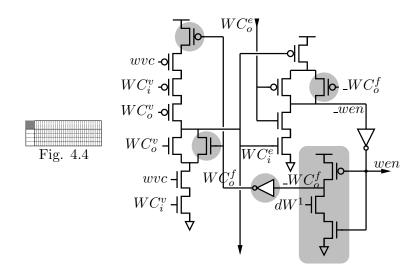

| 4.12         | Pipeline-locked read control propagation.                                       | 70       |

| 4.13         | Pipeline-locked write control propagation.                                      | 70       |

| 4.14         | Read and write data interface for a single port of a bit line                   | 71       |

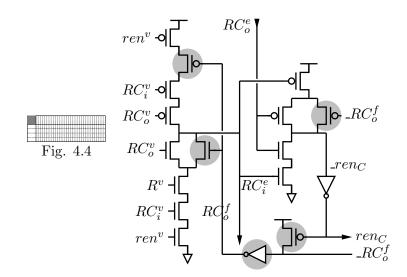

| 4.15         | Read handshake control for full-buffered unconditional control prop-            |          |

|              | agation                                                                         | 73       |

| 4.16         | Read handshake control for half-buffered unconditional control prop-            |          |

|              | agation                                                                         | 73       |

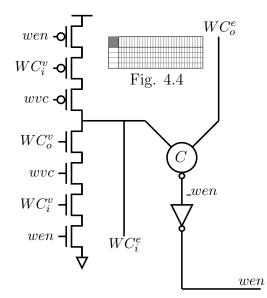

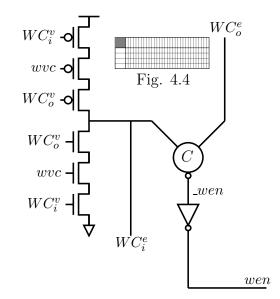

| 4.17         | Write handshake control for full-buffered unconditional control prop-           |          |

|              | agation                                                                         | 74       |

| 4.18         | Write handshake control for half-buffered unconditional control prop-           |          |

|              | agation                                                                         | 74       |

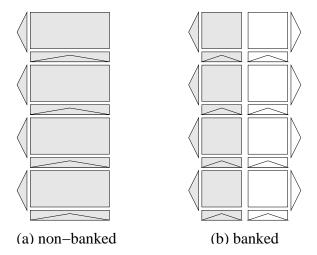

| 4.19         | Banking the register file is a common method for reducing access                |          |

|              | energy and delay by reducing the load on bit lines                              | 77       |

| 4.20         | Block diagram of vertically pipelined, banked read and write pro-               |          |

|              | cesses                                                                          | 78       |

| 4.21         | Bypass decomposition for dual-banked register core                              | 79       |

| F 1          | Constabions activity in man width a damation and width a damation and           |          |

| 5.1          | Switching activity in non-width-adaptive and width-adaptive reg-<br>ister files | 89       |

| 5.0          |                                                                                 | 89<br>91 |

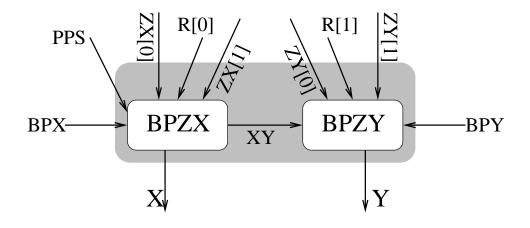

| $5.2 \\ 5.3$ | Examples of width-adaptive representation of integers                           | 91       |

| 0.0          | Block diagram of a width-adaptive register core a) read port and                | 94       |

| 5.4          | b) write port                                                                   | 94<br>98 |

| $5.4 \\ 5.5$ | Floor decomposition of a PCEVHB WAD read port                                   | 98<br>98 |

| 5.6          | Floor decomposition of a PCEVFB WAD write port (unconditional                   | 30       |

| 0.0          | write-enable)                                                                   | 99       |

| 5.7          | Floor decomposition of a PCEVHB WAD write port (unconditional                   | 55       |

| 0.1          | write-enable)                                                                   | 99       |

| 5.8          | Floor decomposition of a PCEVFB WAD write port (conditional                     | 55       |

| 0.0          | write-enable)                                                                   | 99       |

| 5.9          | Floor decomposition of a PCEVHB WAD write port (conditional                     | 00       |

| 0.0          | write-enable)                                                                   | 99       |

| 5.10         |                                                                                 | 100      |

| 5.11         | WAD pipeline-locked write control propagation, for unconditional                | 100      |

| 0.11         |                                                                                 | 101      |

| 5.12         |                                                                                 | 103      |

| 5.13         |                                                                                 | 103      |

| 5.14         | WAD write handshake control, unconditional write-enable, PCEVFB                 |          |

| 5.15         | WAD write handshake control, unconditional write-enable, PCEVHB                 |          |

| 5.16         |                                                                                 | 106      |

| 5.17         |                                                                                 | 106      |

| · · - ·      | ······································                                          |          |

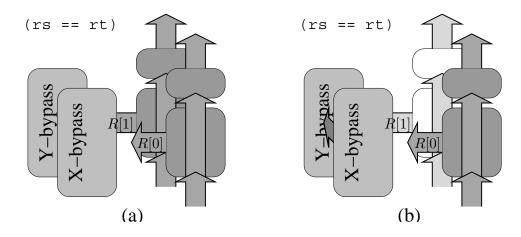

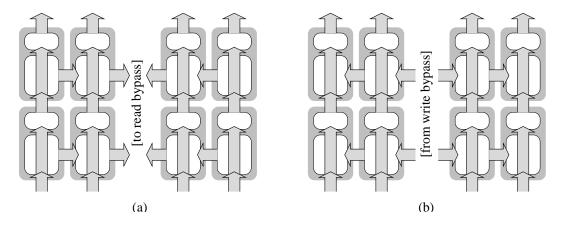

| 7.1  | a) A traditional multi-ported register file may retrieve the same<br>register through different ports, whereas b) a PPS implementation<br>may reduce energy by suppressing redundant read accesses to the |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | core                                                                                                                                                                                                      | 123 |

| 7.2  | Modified read by<br>pass decomposition for Port Priority Selection                                                                                                                                        | 125 |

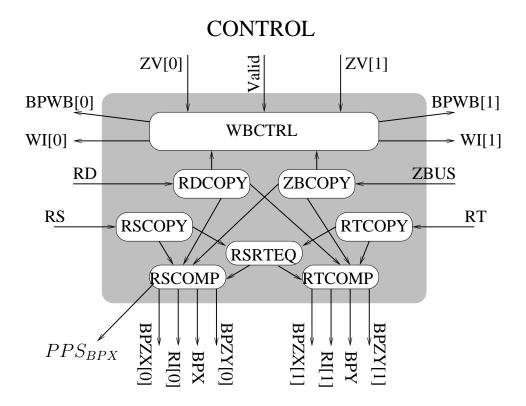

| 7.3  | Schematic of Control decomposition for port priority select                                                                                                                                               | 126 |

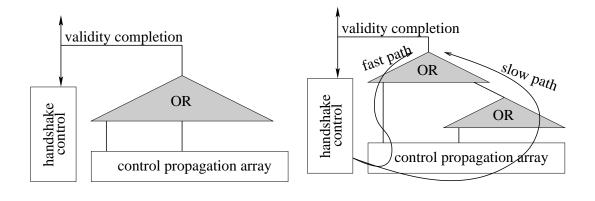

| 8.1  | Balanced and unbalanced completion trees                                                                                                                                                                  | 133 |

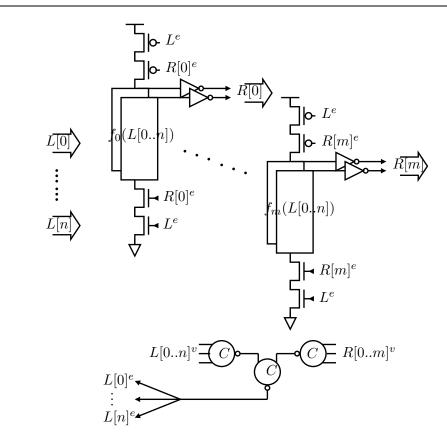

| 9.1  | Block diagram of vertically pipelined, and nested read and write                                                                                                                                          |     |

| 5.1  | processes                                                                                                                                                                                                 | 146 |

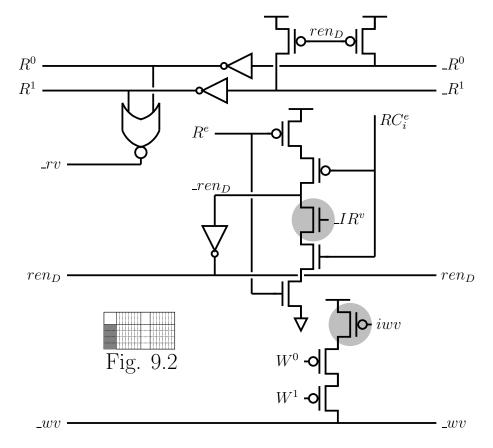

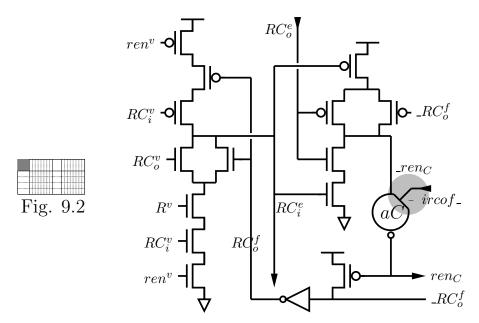

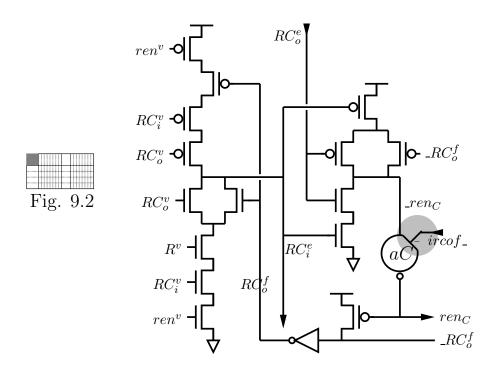

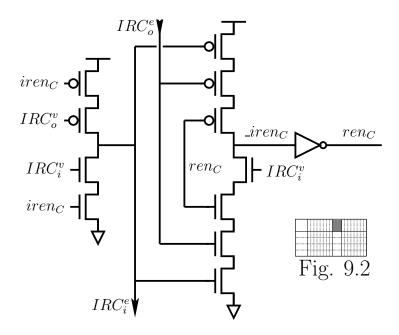

| 9.2  | Floorplan of a nested 4-bit x 16-word pipeline block of the register                                                                                                                                      | 140 |

| 0.2  |                                                                                                                                                                                                           | 154 |

| 9.3  | Floor decomposition of a data-nested core read port                                                                                                                                                       |     |

| 9.4  | · · ·                                                                                                                                                                                                     | 155 |

| 9.5  | Floor decomposition of a PCEVFB nested read port                                                                                                                                                          |     |

| 9.6  | · ·                                                                                                                                                                                                       | 156 |

| 9.7  | Floor decomposition of a PCEVFB nested write port                                                                                                                                                         |     |

| 9.8  | Floor decomposition of a PCEVHB nested write port                                                                                                                                                         |     |

| 9.9  | Floor decomposition of a PCEVFB WAD nested read port                                                                                                                                                      |     |

| 9.10 | Floor decomposition of a PCEVHB WAD nested read port                                                                                                                                                      |     |

| 9.11 | Floor decomposition of a PCEVFB WAD nested write port, (un-                                                                                                                                               |     |

|      | conditional outer write-enable)                                                                                                                                                                           | 167 |

| 9.12 | Floor decomposition of a PCEVHB WAD nested write port, (con-                                                                                                                                              |     |

|      | ditional outer write-enable)                                                                                                                                                                              | 168 |

| 9.13 | Floor decomposition of a PCEVFB WAD nested write port, (con-                                                                                                                                              |     |

|      | ditional outer write-enable)                                                                                                                                                                              | 169 |

| 9.14 | Floor decomposition of a PCEVHB WAD nested write port, (con-                                                                                                                                              |     |

|      | ditional outer write-enable)                                                                                                                                                                              | 170 |

| 9.15 | The interconnect circuit between inner and outer register partitions                                                                                                                                      |     |

|      | for a single nested read port                                                                                                                                                                             | 172 |

| 9.16 | The interconnect circuit between inner and outer register partitions                                                                                                                                      |     |

|      | for a single nested write port                                                                                                                                                                            | 173 |

| 9.17 | Data interface cell for nested reading and writing                                                                                                                                                        |     |

| 9.18 | PCEVFB WAD nested read handshake control circuit                                                                                                                                                          | 175 |

| 9.19 | PCEVHB WAD nested read handshake control circuit                                                                                                                                                          | 176 |

| 9.20 | The control interconnect circuit between the inner and outer par-                                                                                                                                         |     |

|      | titions' control propagation arrays for a non-WAD nested read port                                                                                                                                        | 177 |

| 9.21 | The control interconnect circuit between the inner and outer par-                                                                                                                                         |     |

|      | titions' control propagation arrays for a WAD nested read port.                                                                                                                                           |     |

|      | Shaded circuits are modifications introduced by WAD                                                                                                                                                       | 177 |

| 9.22 | The control interconnect circuit between inner and outer partitions'                                                                                                                                      |     |

|      | control propagation arrays for a non-WAD nested write port                                                                                                                                                | 178 |

| 9.23 | The control interconnect circuit between the inner and outer par-   |

|------|---------------------------------------------------------------------|

|      | titions' control propagation arrays for a WAD nested write port     |

|      | with an unconditional outer write-enable. The shaded circuits are   |

|      | modifications introduced by WAD                                     |

| 9.24 | The control interconnect circuit between the inner and outer parti- |

|      | tions' control propagation arrays for a WAD nested write port with  |

|      | a conditional outer write-enable. The shaded circuits are modifica- |

|      | tions introduced by WAD                                             |

| 9.25 | Vertically pipelined, banked and nested read and write ports 181    |

# List of Programs

| 1.1  | Equivalent HSEs: precharge half-buffer (PCHB)                            |

|------|--------------------------------------------------------------------------|

| 1.2  | Equivalent HSEs: precharge full-buffer (PCFB)                            |

| 1.3  | HSE of a PCHB template for a function of multiple inputs and             |

|      | multiple outputs                                                         |

| 2.1  | CHP: register file                                                       |

| 2.2  | CHP: register file with explicit bypass                                  |

| 2.3  | CHP: register core                                                       |

| 2.4  | CHP: register file bypass (sequential)                                   |

| 2.5  | CHP: register file control                                               |

| 2.6  | CHP: core read port 23                                                   |

| 2.7  | CHP: core write port                                                     |

| 2.8  | CHP: read port demux                                                     |

| 2.9  | CHP: single-register read port                                           |

| 2.10 | CHP: write port demux                                                    |

| 2.11 | CHP: single-register write port                                          |

| 2.12 | CHP: register file control, after rolling back one writeback phase 28    |

| 3.1  | CHP: template for an unpipelined process                                 |

| 3.2  | CHP: template for a non-CRT vertically pipelined process 40              |

| 3.3  | CHP: template for a CRT vertically pipelined process, with inde-         |

|      | pendent actions                                                          |

| 3.4  | CHP: template for a non-CRT vertically pipelined process, with           |

|      | locking                                                                  |

| 3.5  | CHP: template for pipelined process with locking at the receivers $.$ 42 |

| 3.6  | CHP: template for pipelined process with locking at the sender $43$      |

| 4.1  | Equivalent HSEs: precharge enable-valid full-buffer (PCEVFB) 48          |

| 4.2  | Equivalent HSEs: precharge enable-valid half-buffer (PCEVHB) 49          |

| 4.3  | HSE: PCEVFB data-independent read port                                   |

| 4.4  | HSE: PCEVFB data-independent read port                                   |

| 4.5  | HSE: PCEVFB data-independent read port                                   |

| 4.6  | HSE: PCEVHB data-independent read port with full-buffered data           |

|      | output, and half-buffered control output                                 |

| 4.7  | HSE: terminal block of read port                                         |

| 4.8  | HSE: PCEVFB data-independent write port                                  |

| 4.9  | HSE: PCEVFB data-independent write port                                  |

| 4.10 | HSE: PCEVHB data-independent write port                                           | 54  |

|------|-----------------------------------------------------------------------------------|-----|

| 4.11 | HSE: terminal block of write port                                                 | 55  |

| 4.12 | HSE: the register read cell array component, set-only                             | 57  |

| 4.13 | HSE: the register read data interface with $\_R$ reset $\ldots$ $\ldots$ $\ldots$ | 57  |

|      | HSE: completion tree for $R^v$ in read port                                       | 58  |

| 4.15 | HSE: the register control propagation array (read and write)                      | 59  |

|      | HSE: completion tree for control propagation array in the read and                |     |

|      | write port                                                                        | 59  |

| 4.17 | HSE: the register read handshake control (full buffer)                            | 60  |

| 4.18 | HSE: the register read handshake control (half buffer)                            | 60  |

| 4.19 | HSE: completion tree for <i>ren</i> signals in read port                          | 60  |

| 4.20 | HSE: the terminal block's read handshake control                                  | 62  |

| 4.21 | HSE: the register write cell array component                                      | 64  |

| 4.22 | HSE: completion tree for <i>wvc</i> in read port                                  | 64  |

| 4.23 | HSE: resetting the write validity bitline                                         | 64  |

| 4.24 | HSE: the register write cell array component (set-only)                           | 64  |

| 4.25 | HSE: the register write handshake control (full buffer)                           | 65  |

| 4.26 | HSE: the register write handshake control (half buffer)                           | 65  |

| 4.27 | HSE: the terminal block's write handshake control                                 | 67  |

| 5.1  | CHP: template for a width-adaptive vertical pipeline, with indepen-               |     |

|      | dent actions                                                                      | 92  |

| 5.2  | CHP: template for a width-adaptive vertically pipeline, with locking              | 93  |

| 5.3  | HSE: PCEVFB WAD pipeline stage template with locking                              | 95  |

| 5.4  | HSE: PCEVHB WAD pipeline stage template with locking                              | 95  |

| 5.5  | HSE: PCEVFB WAD pipeline stage template with locking and con-                     |     |

|      | ditional internal enable.                                                         | 97  |

| 9.1  | CHP: template for pipelined, non-WAD, nested process with locking                 |     |

|      | at the sender                                                                     | 147 |

| 9.2  | CHP: template for pipelined, WAD, nested process with locking at                  |     |

|      | the sender                                                                        | 148 |

| 9.3  | HSE: data component of read port with nested data, after final                    |     |

|      | transformations                                                                   | 159 |

| 9.4  | HSE: PCEVFB control component only of the data-independent                        |     |

|      | read port with nested data                                                        | 163 |

| 9.5  | HSE: PCEVFB control component of WAD read port with nested                        |     |

|      | data                                                                              | 165 |

| B.1  | CHP: register file writeback bypass                                               | 207 |

| B.2  | CHP: register file read bypass                                                    | 208 |

| B.3  | CHP: pipelined register file read bypass                                          | 209 |

| B.4  | CHP: pipelined register file writeback bypass                                     | 209 |

| B.5  | CHP: WAD read bypass                                                              |     |

| B.6  | CHP: WAD writeback process                                                        | 210 |

| B.7  | CHP: register file read bypass with source for hard-wired zero                    | 211 |

| B.8  | CHP: read bypasses with port priority select                                      | 212 |

| B.9 CHP: register file read bypass, for a dual-banked core                | 213 |

|---------------------------------------------------------------------------|-----|

| B.10 CHP: register file writeback bypass, for dual-banked register core . | 213 |

| C.1 CHP: register bypass control for base design                          | 215 |

| C.2 CHP: register writeback control of base design                        | 216 |

| C.3 CHP: destination copy process                                         | 216 |

| C.4 CHP: register bypass control for dual-banked register core            | 217 |

| C.5 CHP: register writeback control for a banked register core            |     |

| C.6 CHP: register bypass control for reading 0 from the bypass            | 219 |

| C.7 CHP: register writeback control                                       | 219 |

| C.8 CHP: priority port comparator                                         | 220 |

| C.9 CHP: register bypass control, with priority port select               | 221 |

| D.1 CHP: unpipelined multiported register                                 | 222 |

| D.2 CHP: pipelined, multiported register block                            | 223 |

| D.3 CHP: pipelined register block with locking                            | 223 |

| D.4 CHP: pipelined register read port with locking at the sender          | 223 |

| D.5 CHP: pipelined register write port with locking at the sender         | 224 |

| D.6 CHP: read port demux, with locking                                    | 224 |

| D.7 CHP: write port demux, with locking                                   | 224 |

| D.8 CHP: pipelined, multiported zero-register block                       | 224 |

| D.9 CHP: WAD read port, without locking in the termination case           | 225 |

| D.10 CHP: WAD register write port, without locking in the terminating     |     |

| case                                                                      | 225 |

| D.11 CHP: nested partitions read, with unconditional pipeline-locked con- |     |

| trol propagation                                                          | 226 |

| D.12 CHP: nested partition write, with unconditional pipeline-locked con- |     |

| trol propagation                                                          | 226 |

| D.13 CHP: read and write demuxes for nested partitioning, port $i$        | 227 |

| D.14 CHP: nested partitions read, with WAD pipeline-locked control        |     |

| propagation                                                               | 228 |

| D.15 CHP: nested partition write, with WAD pipeline-locked control prop-  |     |

| agation                                                                   | 229 |

| E.1 HSE: PCEVFB WAD read port                                             | 231 |

| E.2 HSE: PCEVHB WAD read port with full-buffered data output, and         |     |

| half-buffered control propagation                                         | 231 |

| E.3 HSE: PCEVFB WAD write port, with unconditional write-enable .         | 231 |

| E.4 HSE: PCEVHB WAD write port, with unconditional write-enable .         | 232 |

| E.5 HSE: PCEVFB WAD write port, with conditional write-enable             | 232 |

| E.6 HSE: PCEVHB WAD write port, with conditional write-enable             | 232 |

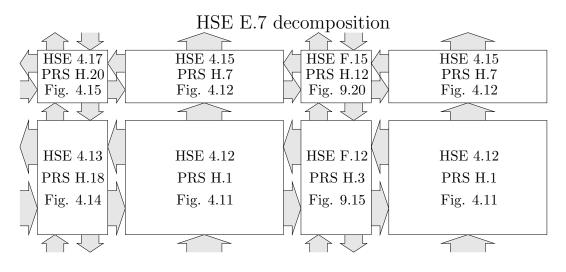

| E.7 HSE: PCEVFB data-independent read port with nested data               | 233 |

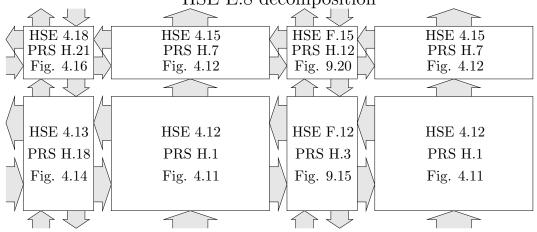

| E.8 HSE: PCEVHB data-independent read port with nested data, full-        |     |

| buffered data output, and half-buffered control propagation               | 234 |

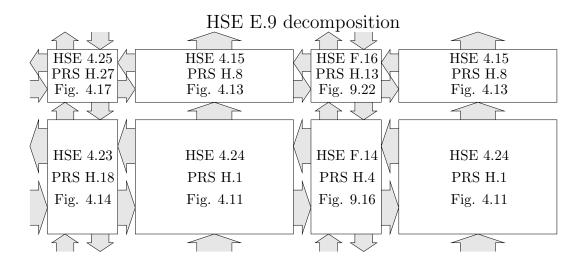

| E.9 HSE: PCEVFB data-independent write port, with nested data             |     |

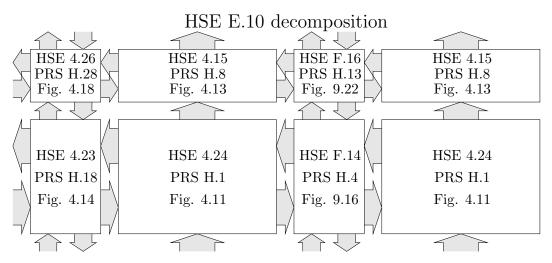

| E.10 HSE: PCEVHB data-independent write port, with nested data            |     |

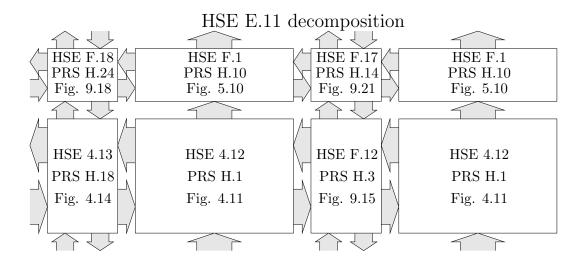

| E.11 HSE: PCEVFB WAD read port with nested data                           |     |

|                                                                           |     |

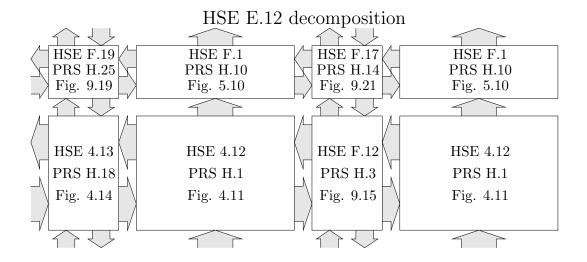

| E.12 | HSE: PCEVHB WAD read port with nested data, full-buffered data               |      |

|------|------------------------------------------------------------------------------|------|

|      | output, and half-buffered control propagation                                | 237  |

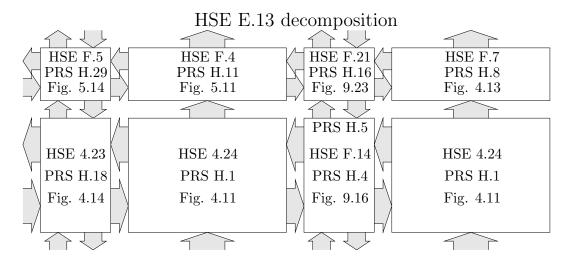

| E.13 | HSE: PCEVFB WAD write port, with nested data, unconditional                  |      |

|      | outer write-enable, conditional inner write-enable variation $\ldots$ .      | 237  |

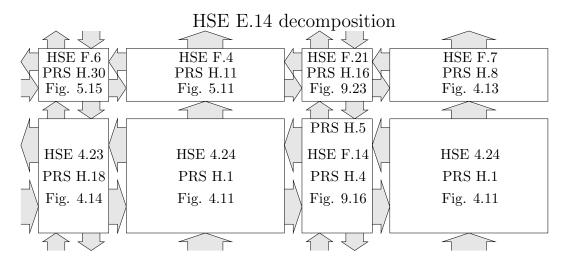

| E.14 | HSE: PCEVHB WAD write port, with nested data, unconditional                  |      |

|      | outer write-enable, conditional inner write-enable variation $\ldots$ .      | 238  |

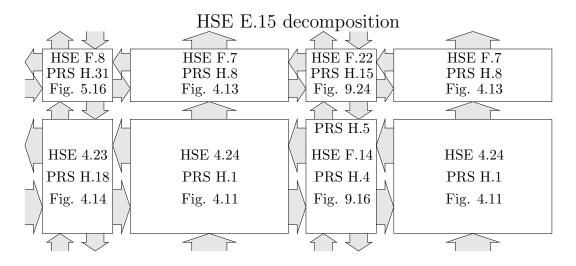

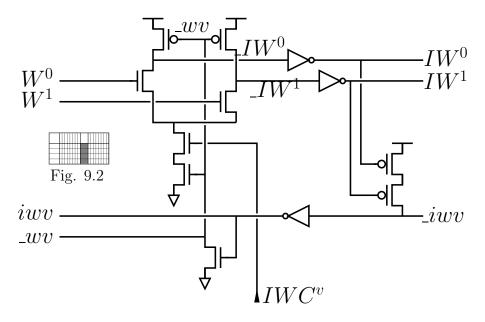

| E.15 | HSE: PCEVFB WAD write port, with nested data, conditional                    |      |

|      | outer write-enable, conditional inner write-enable variation $\ldots$ .      | 238  |

| E.16 | HSE: PCEVFB WAD write port, with nested data, conditional                    |      |

|      | outer write-enable, conditional inner write-enable variation $\ldots \ldots$ | 239  |

| F.1  | HSE: WAD read control propagation array, where the termination               |      |

|      | condition only sets $RC_o^f$                                                 | 241  |

| F.2  | HSE: WAD read handshake control (full buffer)                                | 241  |

| F.3  | HSE: WAD read handshake control (full buffered propagation, half-            |      |

|      | buffered termination)                                                        | 241  |

| F.4  | HSE: the WAD write control propagation array, for unconditional              |      |

|      | write-enable                                                                 | 242  |

| F.5  | HSE: WAD write handshake control, with unconditional write-enable            |      |

| -    | (full buffer)                                                                | 242  |

| F.6  | HSE: WAD write handshake control, with unconditional write-enable            |      |

|      | (full buffer propagation, half buffer termination)                           | 242  |

| F.7  | HSE: WAD write control propagation array, with conditional write-            | 0.40 |

| БО   | enable                                                                       | 243  |

| F.8  | HSE: WAD write handshake control, conditional write-enable (full             | 049  |

| F.9  | buffer)                                                                      | 243  |

| г.9  | buffer)                                                                      | 243  |

| F 10 | HSE: the register read data interface with $\_R$ reset, modified for use     | 240  |

| 1.10 | with nested data arrays                                                      | 244  |

| F 11 | HSE: resetting the write validity bitline                                    | 244  |

|      | HSE: the nested interconnect component between the inner and                 | 411  |

| 1.12 | outer partition of the nested read port data array                           | 245  |

| F.13 | HSE: a single bit of the data component of a data-independent                | - 10 |

|      | control-data join, with nested data                                          | 245  |

| F.14 | HSE: the nested interconnect component between the inner and                 |      |

|      | outer partition of the nested write port array                               | 245  |

| F.15 | HSE: nested interconnect component between the inner and outer               |      |

|      | partitions' non-WAD read control propagation arrays                          | 246  |

| F.16 | HSE: nested interconnect component between the inner and outer               |      |

|      | partitions' non-WAD write control propagation arrays                         | 246  |

| F.17 | HSE: nested interconnect component between the inner and outer               |      |

|      | partitions' WAD read control propagation arrays                              | 247  |

| F.18 | HSE: WAD nested read handshake control (full buffer)                         | 247  |

| F.19 | HSE: WAD nested read handshake control (full-buffered propaga-                                                            |     |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

|      |                                                                                                                           | 247 |

| F.20 | HSE: the nested interconnect component between the delimiter bit                                                          |     |

|      | of the inner and outer partition of the nested write port array                                                           | 248 |

| F.21 | HSE: control nested interconnect between inner and outer partitions                                                       |     |

|      | of WAD nested write handshake control, unconditional outer write-                                                         |     |

|      | enable                                                                                                                    | 248 |

| F.22 | HSE: control nested interconnect between inner and outer partitions                                                       |     |

|      | of WAD nested write handshake control, conditional outer write-                                                           |     |

|      |                                                                                                                           | 248 |

| H.1  | PRS: core register cell, single ported                                                                                    |     |

| H.2  |                                                                                                                           | 255 |

| H.3  | PRS: delay-insensitive interface cell bewteen the data bits of inner                                                      |     |

| 11.0 | and outer banks of a nested register array, shown for a single read                                                       |     |

|      |                                                                                                                           | 256 |

| H.4  | PRS: delay-insensitive interface cell bewteen the data bits of inner                                                      | 200 |

| 11.4 | and outer banks of a nested register array, shown for a single write                                                      |     |

|      |                                                                                                                           | 257 |

| ΠE   | port                                                                                                                      | 201 |

| п.э  |                                                                                                                           |     |

|      | ner and outer banks of a nested register array, used with conditional                                                     |     |

| II a |                                                                                                                           | 257 |

| H.6  | PRS: delay-insensitive interface cell bewteen the delimiter bits of                                                       |     |

|      | inner and outer banks of a nested register array, used with uncon-                                                        |     |

|      | ditional outer write-enable, shown for a single write port                                                                | 258 |

| H.7  | PRS: unconditional read control propagation with locking, for two                                                         |     |

|      |                                                                                                                           | 259 |

| H.8  | PRS: unconditional write control propagation with locking, for two                                                        |     |

|      |                                                                                                                           | 259 |

| H.9  | PRS: unconditional read/write control propagation without locking                                                         |     |

|      | (for register 0), for a single port $\ldots \ldots \ldots$ | 259 |

| H.10 | PRS: WAD conditional read control propagation with locking, for                                                           |     |

|      | two ports with $p = 0, 1$ $(q = 1 - p)$                                                                                   | 260 |

| H.11 | PRS: WAD conditional write control propagation with locking, and                                                          |     |

|      | unconditional write-enable wen, for two ports with $p = 0, 1$ $(q = 1 - p)$                                               | 260 |

| H.12 | PRS: delay-insensitive interface cell between inner and outer banks                                                       |     |

|      |                                                                                                                           | 261 |

| H.13 | PRS: delay-insensitive interface cell between inner and outer banks                                                       |     |

|      |                                                                                                                           | 261 |

| H.14 | PRS: delay-insensitive interface cell between inner and outer banks                                                       |     |

|      | of nested, WAD read control propagation array, single port                                                                | 262 |

| H.15 | PRS: delay-insensitive interface cell between inner and outer banks                                                       |     |

| 0    | of nested, WAD write control propagation array, with conditional                                                          |     |

|      |                                                                                                                           | 262 |

|      |                                                                                                                           |     |

| H.16 PRS: delay-insensitive interface cell between inner and outer banks                      |     |

|-----------------------------------------------------------------------------------------------|-----|

| of nested, WAD write control propagation array, with unconditional                            | 000 |

|                                                                                               | 262 |

| H.17 PRS: delay-insensitive interface cell between inner and outer banks                      |     |

| of nested, WAD write control propagation array, with unconditional                            | ററാ |

|                                                                                               | 263 |

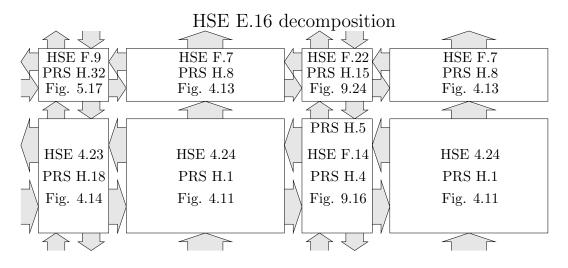

| , 0 I                                                                                         | 264 |

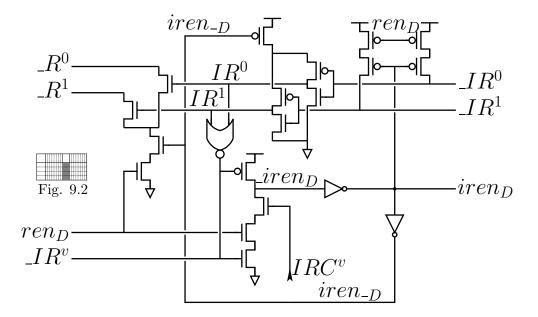

| H.19 PRS: read/write data interface cell for a single port of a nested bit line               | 265 |

|                                                                                               | 200 |

| H.20 PRS: read handshake control for unconditional control propagation,<br>PCEVFB reshuffling | 266 |

| PCEVFB reshuffling                                                                            | 200 |

|                                                                                               | 266 |

| H.22 PRS: read handshake control for WAD conditional control propaga-                         | 200 |

|                                                                                               | 267 |

| H.23 PRS: read handshake control for WAD conditional control propaga-                         | 201 |

|                                                                                               | 267 |

| H.24 PRS: read handshake control for nested, WAD conditional control                          | 201 |

|                                                                                               | 268 |

| H.25 PRS: read handshake control for nested, WAD conditional control                          | 200 |

|                                                                                               | 268 |

|                                                                                               | 269 |

| H.27 PRS: write handshake control for unconditional control propagation,                      | 200 |

| PCEVFB reshuffling                                                                            | 270 |

| H.28 PRS: write handshake control for unconditional control propagation,                      |     |

| 1 1 0 /                                                                                       | 270 |

| H.29 PRS: write handshake control for WAD control propagation, with                           |     |

|                                                                                               | 271 |

| H.30 PRS: write handshake control for WAD control propagation, with                           |     |

| unconditional write-enable <i>wen</i> , PCEVHB reshuffling                                    | 271 |

| H.31 PRS: write handshake control for WAD control propagation, with                           |     |

| conditional write-enable wen, PCEVFB reshuffling                                              | 272 |

| H.32 PRS: write handshake control for WAD control propagation, with                           |     |

| conditional write-enable wen, PCEVHB reshuffling                                              | 272 |

| H.33 PRS: write handshake control for control termination                                     | 273 |

## List of Abbreviations

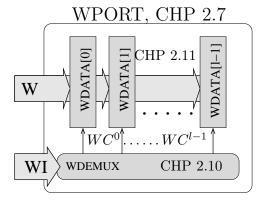

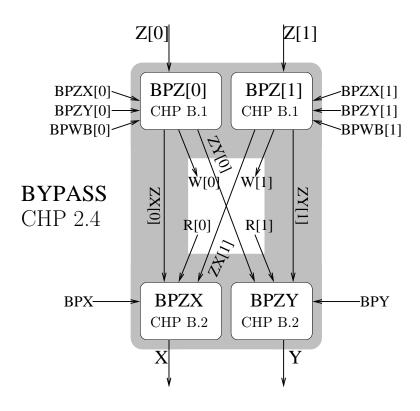

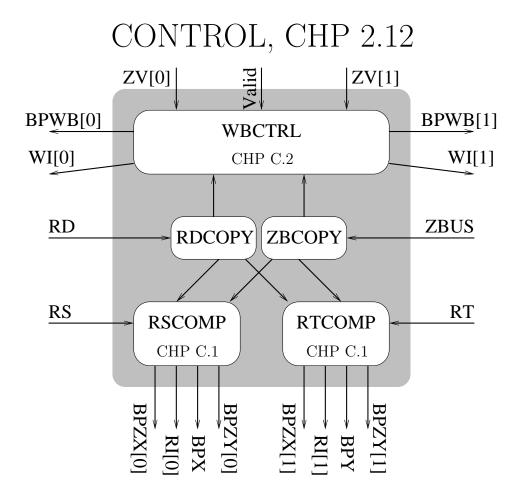

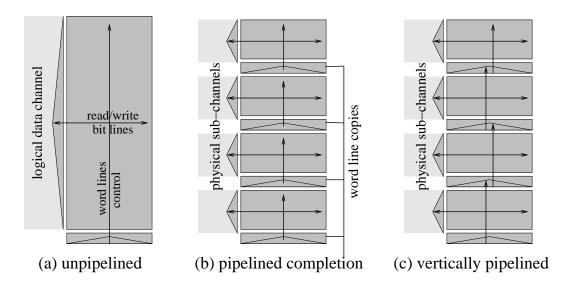

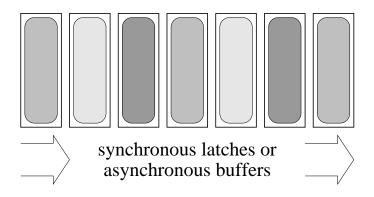

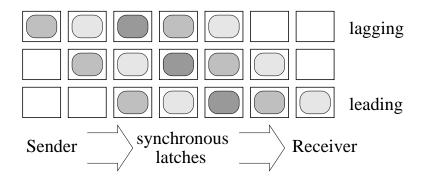

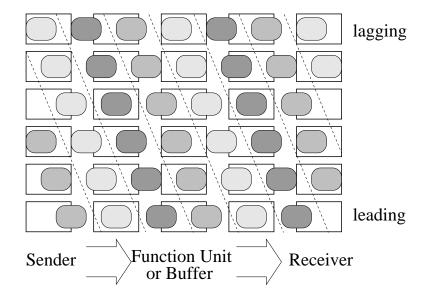

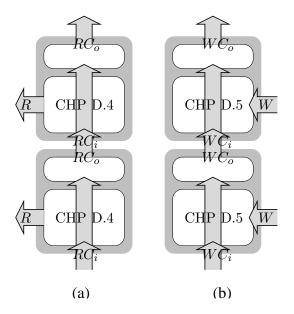

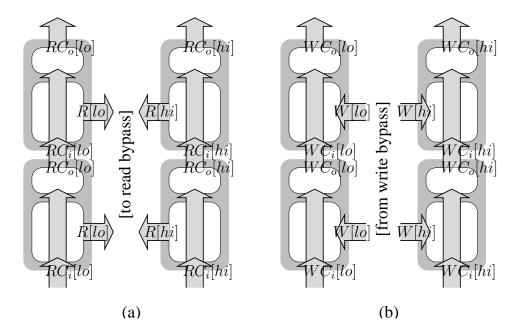

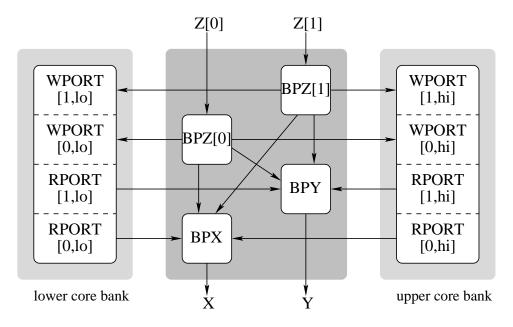

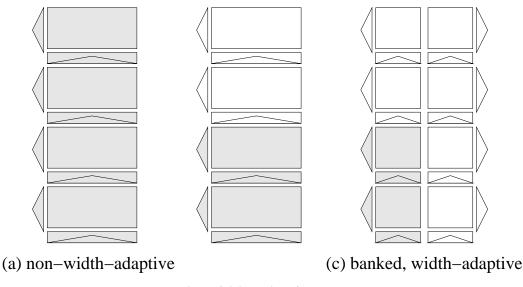

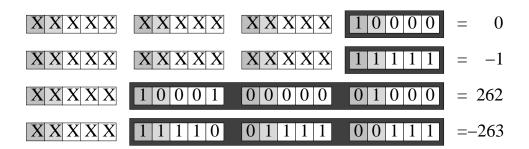

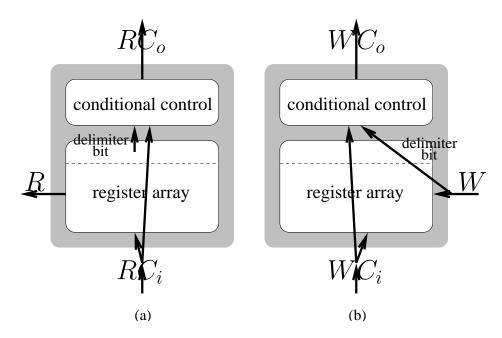

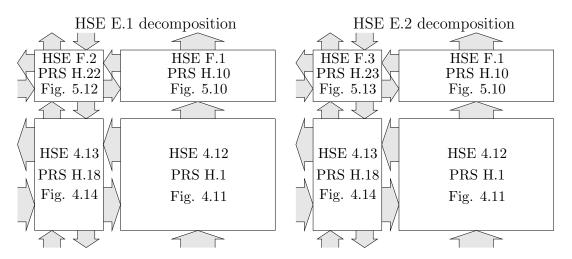

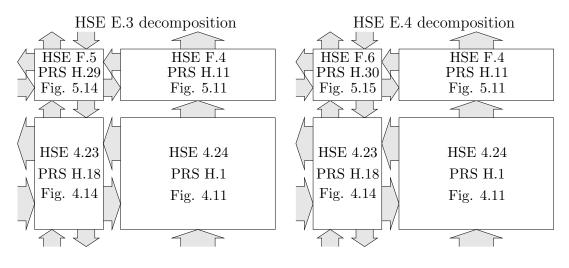

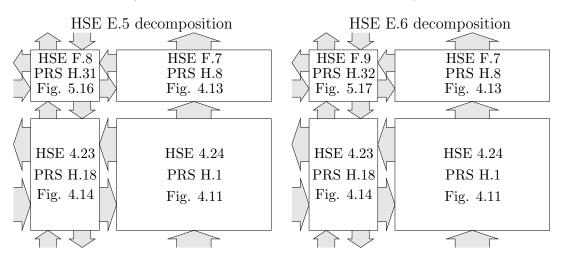

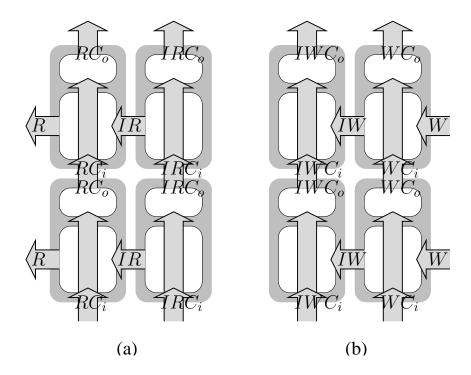

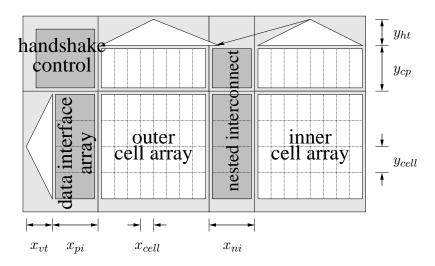

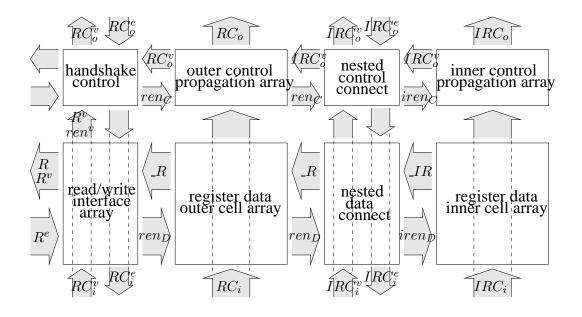

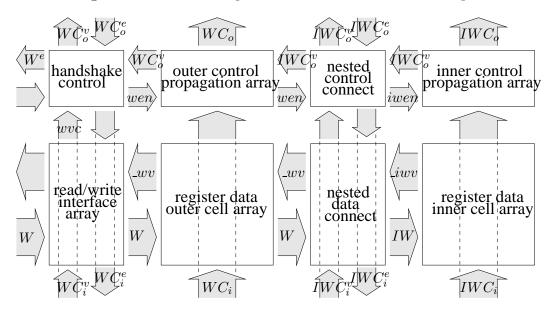

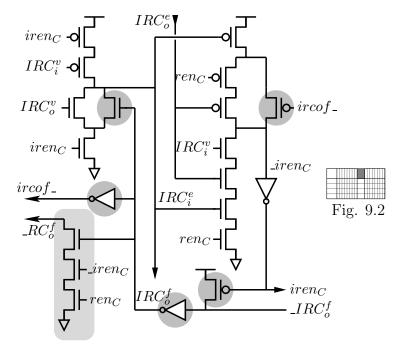

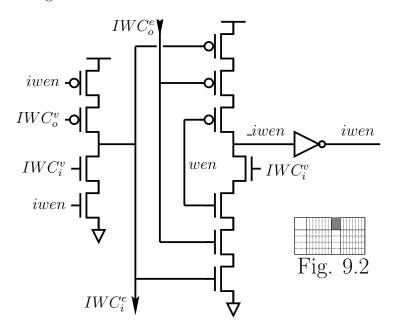

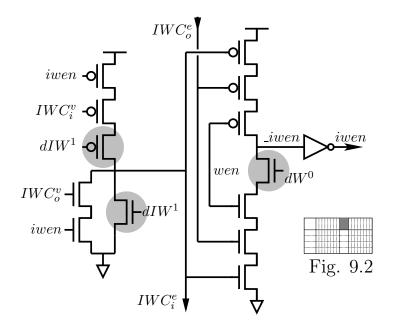

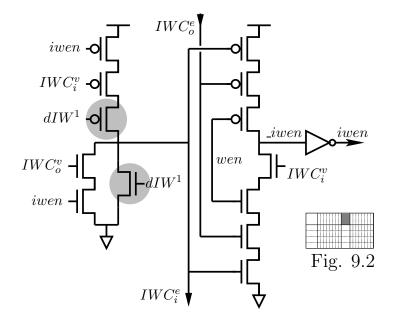

| CHP<br>CMOS<br>CRT<br>DRAM<br>HSE<br>ISA<br>ILP<br>NFET<br>PFET<br>PCEVFB<br>PCEVHB<br>PCFB<br>PCFB<br>PCHB<br>PBS | Concurrent Hardware Processes<br>complementary metal-oxide semiconductor<br>constant response time<br>dynamic random access memory<br>handshaking expansion<br>instruction set architecture<br>instruction-level parallelism<br>n-diffusion field effect transistor<br>p-diffusion field effect transistor<br>precharge enable-valid full-buffer (Section 4.1)<br>precharge enable-valid half-buffer (Section 4.1)<br>precharge full-buffer (Section 1.1)<br>precharge half-buffer (Section 1.1) |